Comp 411 - Fall 2018

### THE GOAL OF PIPELINING

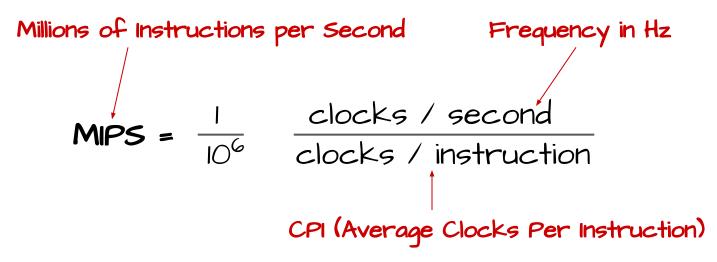

• Recall our measure of processor performance

• How can we turn up the clock rate?

#### GOAL OF PIPELINING

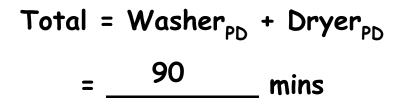

Function: Fill, Agitate, Spin Washer<sub>PD</sub> = 30 mins

Device: Dryer Function: Heat, Spin Dryer<sub>PD</sub> = 60 mins

Device: Washer

#### 11/26/2018

# ONE LOAD AT A TIME

Everyone knows that the real reason that UNC students put off doing laundry so long is \*not\* because they procrastinate, are lazy, or even have better things to do.

The fact is, doing laundry one load at a time is not smart.

(Sorry Mom, but you were wrong about this one!)

```

Step 1:

```

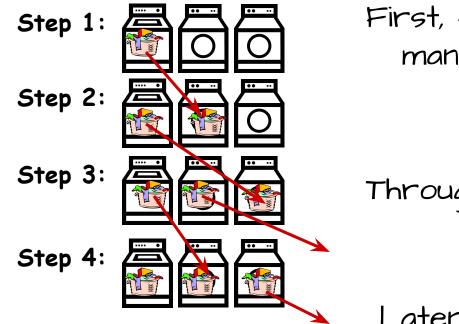

### DOING N LOADS OF LAUNDRY

Here's how they do laundry at Duke, the "combinational" way.

(Actually, this is just an urban legend. No one at Duke actually does laundry. The butler's all arrive on Wednesday morning, pick up the dirty laundry and return it all pressed and starched by dinner)

Step 3:

Step 1:

Step 2:

Step 4:

Total = N\*(Washer<sub>PD</sub> + Dryer<sub>PD</sub>) = <u>N\*90</u> mins

Comp 411 - Fall 2018

# DOING N LOADS ... THE UNC WAY

UNC students "pipeline" the laundry process.

That's why we wait!

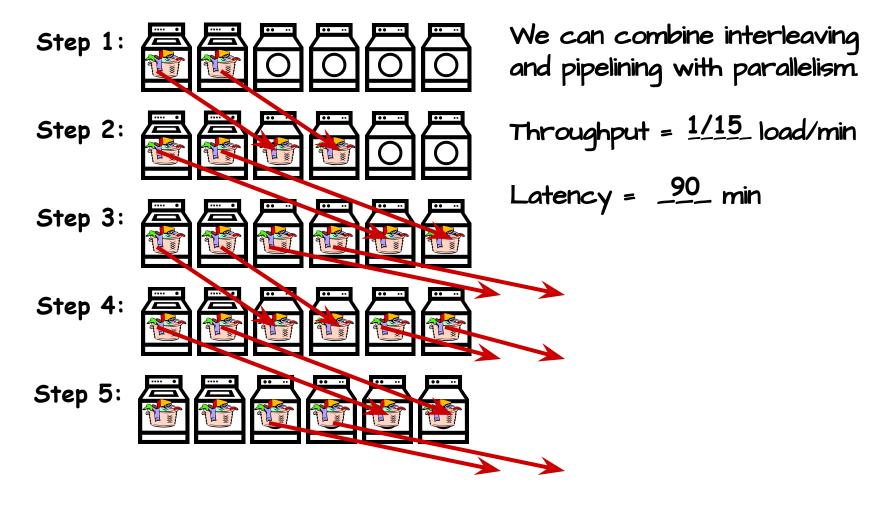

Actually, it's more like N\*GO + 30 if we account for the startup transient correctly. When doing pipeline analysis, we're mostly interested in the "steady state" where we assume we have an infinite supply of inputs. Step 1:

Step 2:

Step 3:

Total = N \* Max(Washer<sub>PD</sub>, Dryer<sub>PD</sub>) = <u>N\*60</u> mins

Latency:

The delay from when an input is established until the output associated with that input becomes valid.

(Duke Laundry = <u>90</u>\_\_\_\_ mins) Assuming that the wash is (UNC Laundry = <u>120</u>\_\_\_\_ mins) started as soon as possible and waits (wet) in the washer until dryer is available.

Throughput:

The rate of which inputs or outputs are processed.

(Duke Laundry =

$$-1/90$$

outputs/min)

(UNC Laundry =  $-1/90$  outputs/min)

$1/60$

Even though we increase latency, it takes less time per load

# OKAY, BACK TO CIRCUITS ...

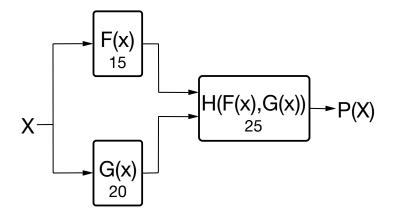

For combinational logic: latency = t<sub>PD'</sub> throughput = 1/t<sub>PD</sub> We can't get the answer faster, but are we making effective use of our hardware at all times?

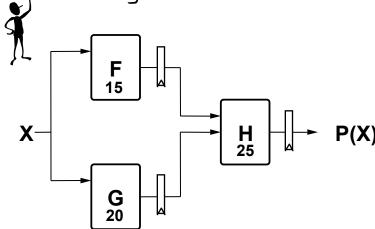

# PIPELINED CIRCUITS

y, use registers to hold H's input stable!

9

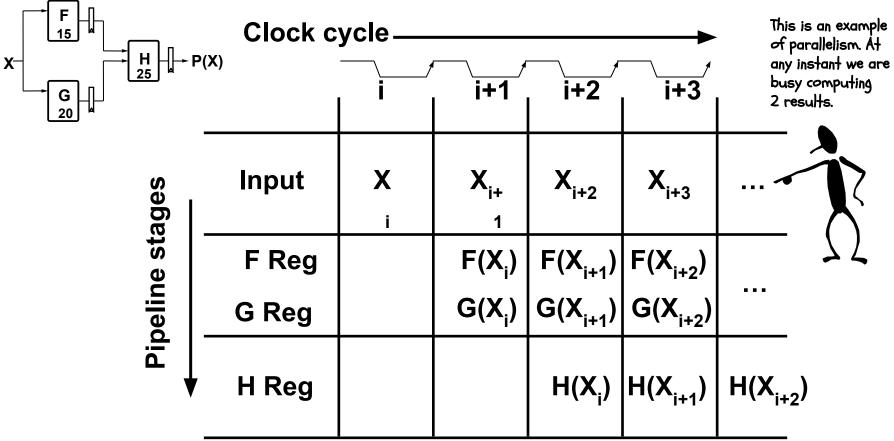

Now F & G can be working on input X<sub>i+1</sub> while H is performing its computation on X<sub>i</sub>. We've created a 2-stage *pipeline*: **P(X)** if we have a valid input X during clock cycle j. P(X) is valid during clock j+2.

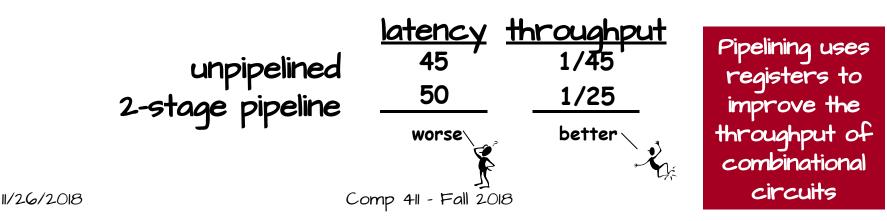

Suppose F, G, H have propagation delays of 15, 20, 25 ns and we are using ideal zero-delay registers ( $t_s = 0, t_{pd} = 0$ ):

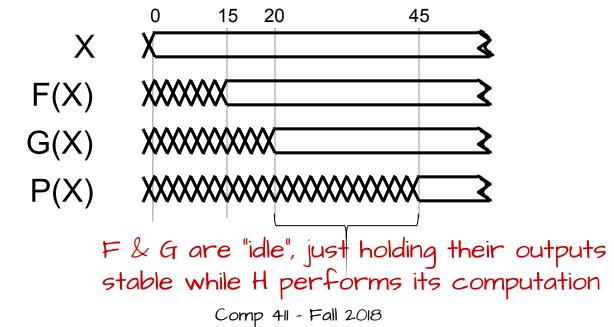

#### PIPELINE DIAGRAMS

A pipeline diagram is just a depiction of what inputs are being processed during a given clock period. The results associated with a particular set of input data move *diagonally* through the diagram, progressing through one pipeline stage on each clock cycle.

# PIPELINE CONVENTIONS

DEFINITION:

A *K-Stage Pipeline* ("K-pipeline") is an acyclic circuit having exactly K registers on every path from an input to an output.

A COMBINATIONAL CIRCUIT is thus a O-stage pipeline. CONVENTION:

Every pipeline stage, hence every K-Stage pipeline, has a register on its OUTPUTS (as opposed to, alternatively, its inputs).

#### ALWAYS:

The CLOCK common to all registers \*must\* have a period sufficient to allow for the propagation delays of all combinational paths PLUS (input) register's t<sub>PD</sub> PLUS (output) register's t<sub>SETUP</sub>.

The LATENCY of a K-pipeline is K times the period of the clock common to all registers.

The THROUGHPUT of a K-pipeline is the frequency of the clock.

# PIPELINING SUMMARY

#### Advantages:

- Higher throughput than combinational system

- Different parts of the logic work on different parts of the problem...

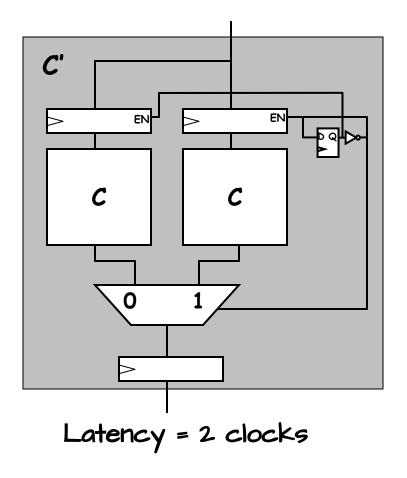

# Disadvantages: - Generally, increases latency - Only as good as the \*weakest\* link. (often called the pipeline's BOTTLENECK) Isn't there a way around this "weak link" problem?

How to work around a bottleneck.

First, find a place with twice as many dryers as washers.

# THIS IS CALLED "INTERLEAVING"

One way to overcome a pipeline bottleneck is to **replicate the critical element** as many times as needed and *alternate* inputs between the various copies.

N-way interleaving is equivalent to how many pipeline Stages? \_\_\_\_

#### BETTER YET ... PARALLELISM

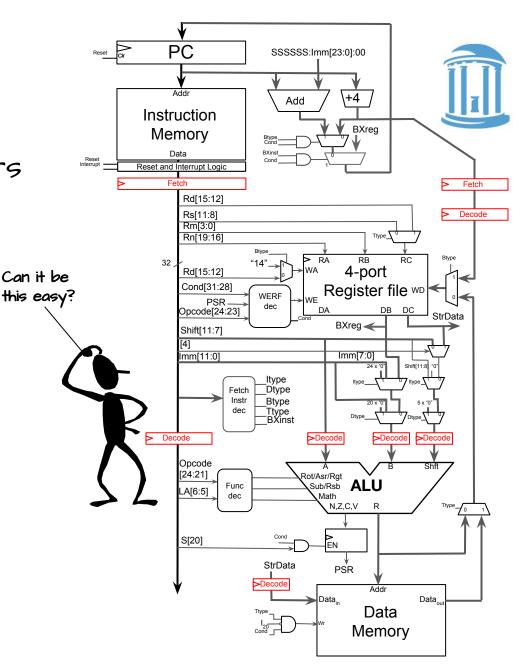

#### HOW TO PIPELINE THIS?

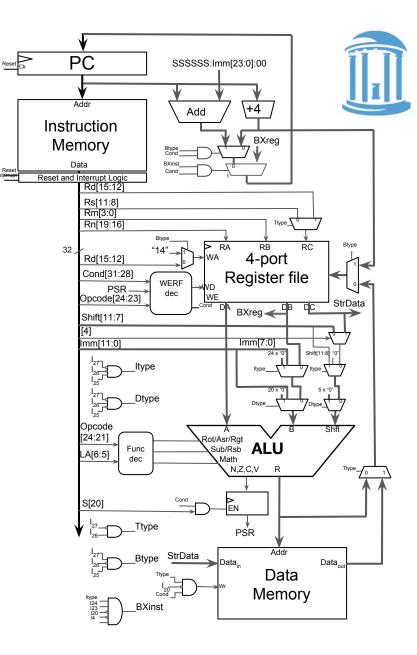

A CPU is a digital circuit like any other. Thus, we should be able to pipeline it to increase its throughput.

However, there are a few tricky issues.

- It already has registers that get updated on each clock (register file, PSR, and PC)

- It has feedback, the ALU or

Data Memory outputs are routed back to the register file

#### 17

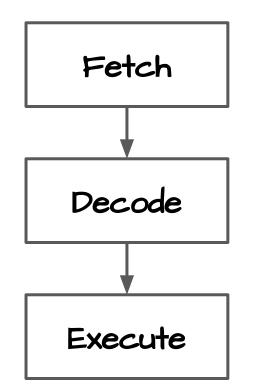

Execute:

ALU operation Write-back register

Instruction memory access Decode: Decode instructions Get register operands

Fetch:

A simple 3-stage pipeline:

### OUR GOAL

# HOW INSTRUCTIONS FLOW

Consider the following instruction sequence:

Progress in a three-stage pipeline

Once filled, at every clock there are 3 instructions at various stages of execution.

| r1,r1,r2 |

|----------|

| r2,r2,#2 |

| r0,r0,#1 |

| r1, r2   |

|          |

Time (in clock cycles)

|          | i                                                                         | i+1                        | i+2                        | i+3                    | i+4          | i+5                     |  |

|----------|---------------------------------------------------------------------------|----------------------------|----------------------------|------------------------|--------------|-------------------------|--|

| Fetch    | sub r1,r1,r2                                                              | add r2,r2,#2               | and r0,r0,#1               | cmp r1,r2              |              | Source<br>operands      |  |

| Decode   |                                                                           | sub r1, <mark>r1,r2</mark> | add r2, <mark>r2,#2</mark> | and r0,r0,#1           | cmpr1,r2     | fetched in<br>this stag |  |

| Execute  |                                                                           |                            | sub 1r1,r2                 | add <sup>2</sup> r2,#2 | and r0,r0,#1 | cmp r1,r2               |  |

| /26/2018 | Destination operands are<br>updated in this stage<br>Comp 411 - Fall 2018 |                            |                            |                        |              |                         |  |

### NEXT TIME

- Three pipeline registers on every datapath from the instruction memory's output to the register file's write data port.

- How much faster?