#### SYNCHRONOUS LOGIC

- 1) Sequential Logic

- 2) Synchronous Design

- 3) Synchronous Timing Analysis

- 4) Single Clock Design

- 5) Finite State Machines

- 6) Mealy and Moore

- 7) State Transition Diagrams

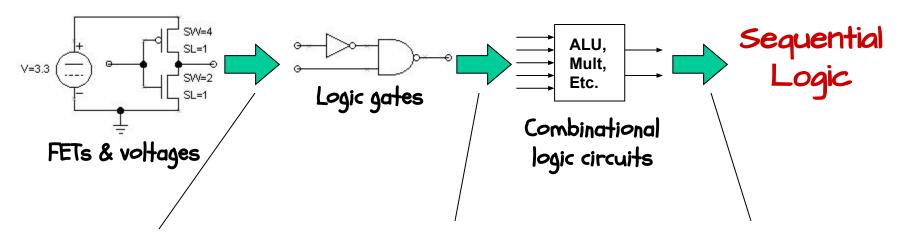

#### ROAD TRAVELED SO FAR...

#### Combinational contract:

- · Voltage-based "bits"

- · 1-bit per wire

- Generate quality outputs,

tolerate inferior inputs

- · Combinational contract

- Complete in/out/timing spec

Acyclic connections Composable blocks Design:

- truth tables

- sum-of-products

- muxes

- ROMs

Storage & state

Dynamic discipline

Finite-state

machines

Throughput &

latency

Pipelining

Our motto: Sweat the details once, and then put a box around it!

#### SOMETHING WE CAN'T BUILD

What if you were given the following system design specification?

When the button is pushed:

- 1) Turn on the light if it is off

- 2) Turn off the light if it is on

The light should change state within a second of the button press

What makes this System so different from those we've discussed before?

1. "State" - i.e. the circuit has memory

light

2. The output was changed by a input "event" (pushing a button) rather than an input "value"

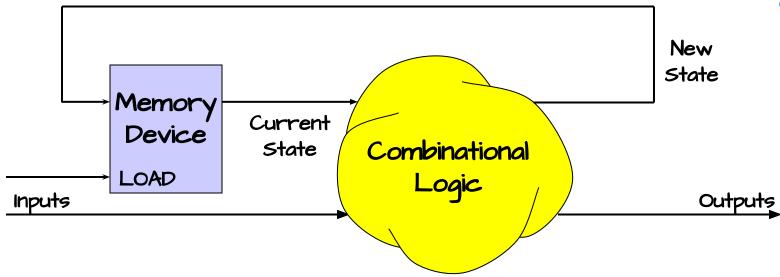

### "SEQUENTIAL" = STATEFUL

Plan: Build a Sequential Circuit with stored digital STATE -

- MEMORY stores CURRENT state

- Combinational Logic computes

- the NEXT state (Based on inputs & current state)

- the OUTPUTs (Based on inputs and/or current state)

- State changes on LOAD control input

Didn't we develop some memory devices last time?

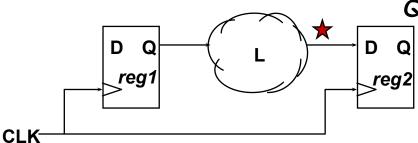

# "SYNCHRONOUS" SINGLE-CLOCK LOGIC III

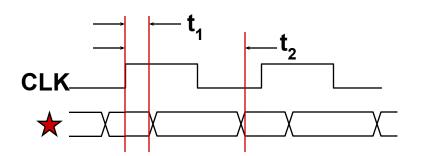

$$t_1 = t_{CD,reg1} + t_{CD,L} \ge t_{HOLD,reg2}$$

$t_2 = t_{PD,reg1} + t_{PD,L} \le t_{CLK} - t_{SETUP,reg2}$

Questions for register-based designs:

- · How much time for useful work (i.e. for combinational logic delay)?

- Does it help to guarantee a minimum t<sub>CD</sub>? How 'bout designing registers so that t<sub>CD,reg</sub> ≥ t<sub>HOLD,reg</sub>?

- What happens if CLK signal doesn't arrive at the two registers at exactly the same time (a phenomenon known as "clock skew")?

Minimum Clock Period :  $t_{CLK} \ge t_{PD,reg1} + t_{PD,L} + t_{SETUP,reg2}$

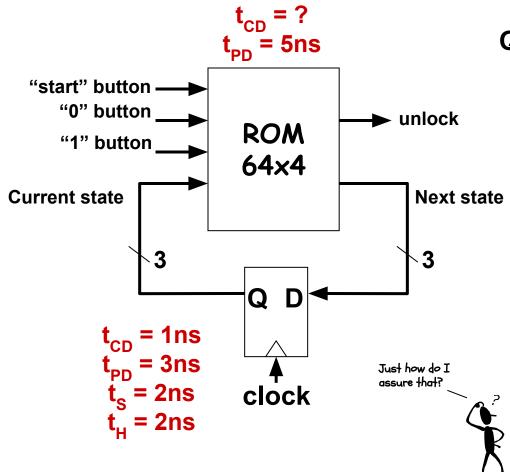

#### EXAMPLE: SYNCHRONOUS TIMING

#### **Questions:**

1. t<sub>cn</sub> for the ROM?

$$\begin{array}{l} t_{\text{CD,REG}} + t_{\text{CD,ROM}} > t_{\text{H,REG}} \\ 1 \text{ ns} + t_{\text{CD,ROM}} > 2 \text{ nS} \\ t_{\text{CD,ROM}} > 1 \text{ nS} \end{array}$$

2. Min. clock period?

$$\begin{aligned} &t_{\text{CLK}} > t_{\text{PD,REG}} + t_{\text{PD,ROM}} + t_{\text{S,REG}} \\ &t_{\text{CLK}} > 3 \text{ ns} + 5 \text{ ns} + 2 \text{ nS} \\ &t_{\text{CLK}} > 10 \text{ nS} \end{aligned}$$

3. Constraints on inputs?

"start", "0", and "1" must be valid  $t_{PD,ROM} + t_{S,REG} = 5 + 2 = 7 \text{ ns}$  before the clock and held  $t_{H,REG} - t_{CD,ROM} = 2 - 1 = 1 \text{ ns}$

## SYNCHRONOUS SINGLE-CLOCK DESIGN

## Sequential # Synchronous

However, Synchronous = A recipe for robust sequential circuits:

- · No combinational cycles (other than those already inside the registers)

- Only cares about values of combinational circuits just before rising edge of clock

- · Clock period greater than every combinational delay

- Changes state after all logic transitions have stopped!

#### DESIGNING SEQUENTIAL LOGIC

Sequential logic is used when the solution to some design problem involves a sequence of steps:

How to open digital combination lock w/3 buttons ("start", "O" and "1"):

Step 1: press "start" button

Step 2: press "0" button

Step 3: press "1" button

Step 4: press "1" button

Step 5: press "0" button

remembered between steps is called state. Might be just what step we're on, or might include results from earlier steps we'll need to complete a later step.

Comp 411 - Fall 2018

3

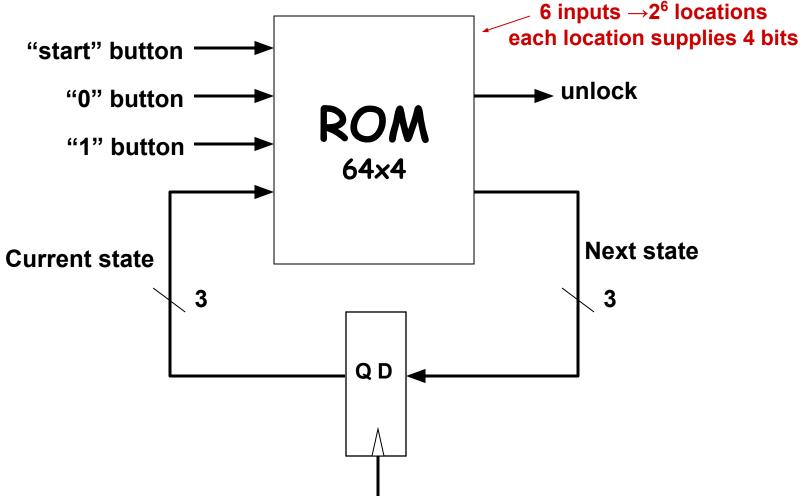

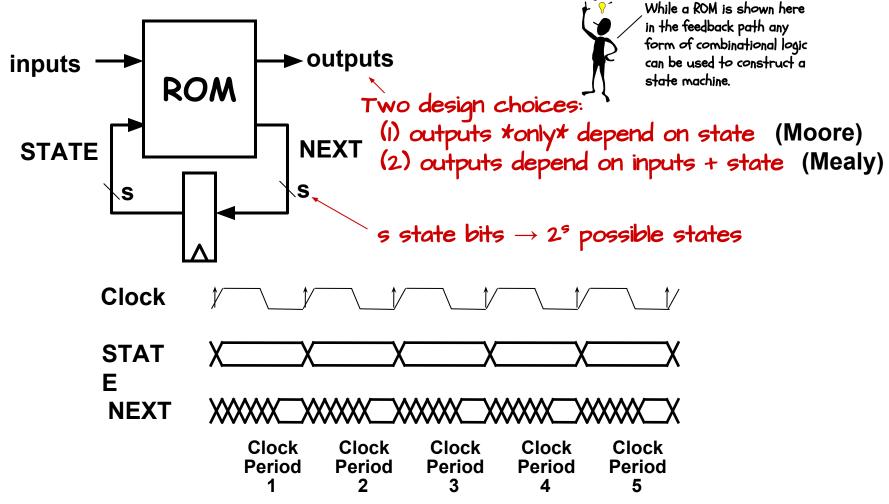

## IMPLEMENTING A "STATE MACHINE"

9

| Current State "start" "1" "0"                                                               |                 |            |   |   |   | Next State unlock |        |            |

|---------------------------------------------------------------------------------------------|-----------------|------------|---|---|---|-------------------|--------|------------|

| This flavor of                                                                              |                 |            | 1 |   |   | start             | 0      | 000        |

| "truth-table" is called a "state-transition table"  This is starting to look like a PROGRAM | start           | 000        | 0 | 0 | 1 | digit1            | 0      | 001        |

|                                                                                             | start           | 000        | 0 | 1 | 0 | error             | 0      | 101        |

|                                                                                             | start           | 000        | 0 | 0 | 0 | start             | 0      | 000        |

|                                                                                             | digit1          | 001        | 0 | 1 | 0 | digit2            | 0      | 010        |

|                                                                                             | digit1          | 001        | 0 | 0 | 1 | error             | 0      | 101        |

|                                                                                             | digit1          | 001        | 0 | 0 | 0 | digit1            | 0      | 001        |

|                                                                                             | digit2          | 010        | 0 | 1 | 0 | digit3            | 0      | 011        |

|                                                                                             | digit3          | 011        | 0 | 0 | 1 | unlock            | 0      | 100        |

|                                                                                             | unlock          | 100        | 0 | 1 | 0 | error             | 1      | 101        |

| K                                                                                           | unlock          | 100        | 0 | 0 | 1 | error             | 1      | 101        |

| \$ 1                                                                                        | unlock<br>error | 100<br>101 | 0 | 0 | 0 | unlock<br>error   | 1<br>0 | 100<br>101 |

6 different states → encode using 3 bits

### NOW, WE DO IT WITH HARDWARE!

Trigger update periodically ("clock")

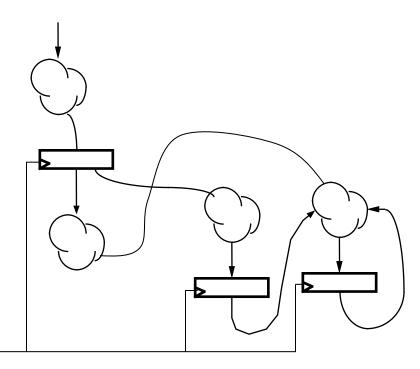

#### A FINITE STATE MACHINE

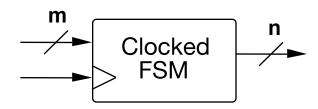

#### A Finite State Machine has:

- k States S<sub>1</sub>, S<sub>2</sub>, ... S<sub>k</sub> (one is the "initial" state)

- m inputs I<sub>1</sub>, I<sub>2</sub>, ... I<sub>m</sub>

- n outputs O<sub>1</sub>, O<sub>2</sub>, ... O<sub>n</sub>

- Transition Rules, S'(S<sub>i</sub>,I<sub>1</sub>, I<sub>2</sub>, ... I<sub>m</sub>)

for each state and input combination

- Output Rules, O(S<sub>i</sub>) for each state

### DISCRETE STATE, DISCRETE TIME

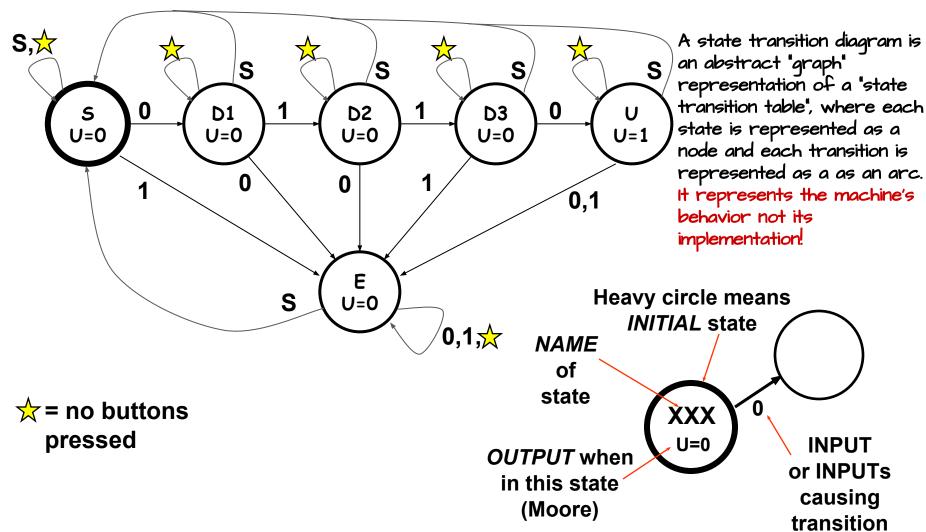

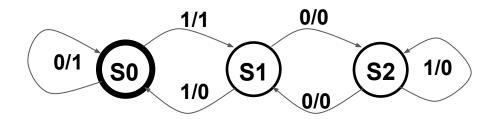

#### STATE TRANSITION DIAGRAMS

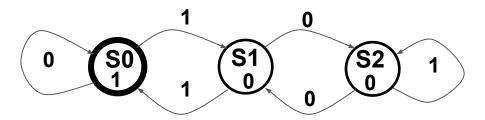

#### EXAMPLE STATE DIAGRAMS

MOORE Machine: Outputs on States

MEALY Machine:

Outputs on Transitions

Arcs leaving a state must be:

(1) mutually exclusive

can only have one choice for any given input value

(2) collectively exhaustive

every state must specify what happens for each possible input combination. "Nothing happens" means are back to itself.

### NEXT TIME

#### Counting state machines