#### PHYSICAL BITS: TRANSISTORS AND LOGIC

- Encoding bits with voltages

- The "Digital" contract

- Digital processing elements

- Gates

- Transistors

- Building gates with transistors

#### WHERE ARE WE?

Things we know so far -1) Computers process information 2) Information is measured in bits 3) Data can be represented as groups of bits 4) Computer instructions are encoded as bits 5) Computer instructions are just data (6) But, we don't want to deal with details of bits... so we use ASSEMBLY Language 7) Even that is too low-level...

So we use COMPILERs to generate assembly code, and assemblers to generate the final bits ...

#### But, how are bits PROCESSED?

Comp 411 - Fall 2018

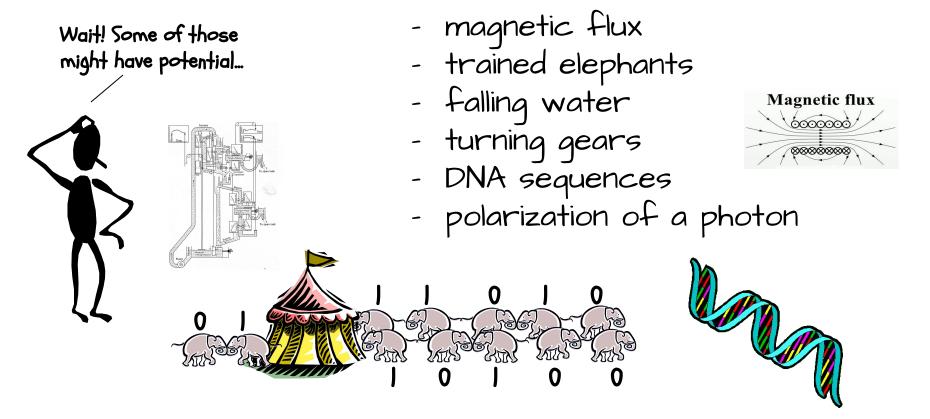

## A SUBSTRATE FOR COMPUTATION

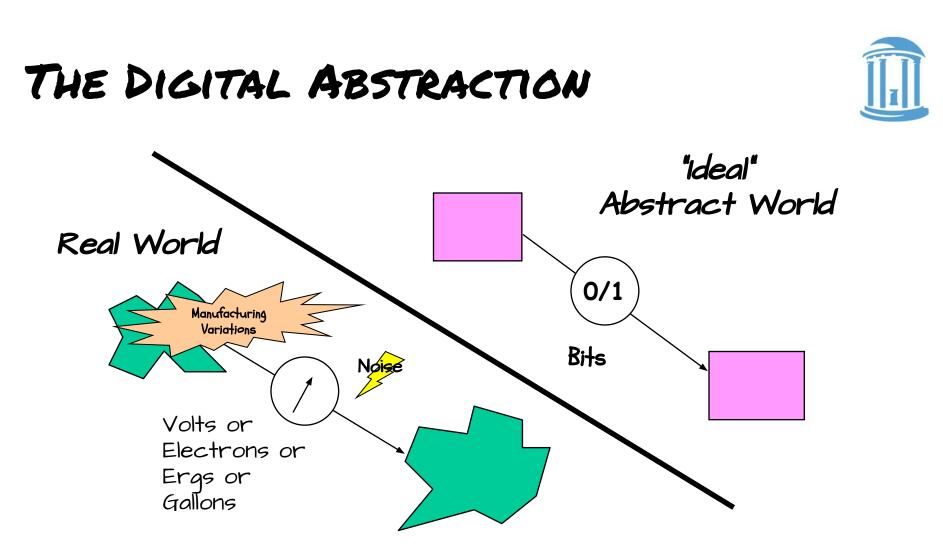

We can build devices for processing and representing bits using almost any physical phenomenon

# USING ELECTROMAGNETIC PHENOMENA

Some EM things we could encode bits with: voltages phase currents frequency With today's technologies voltages are most often used. Voltage pros: easy generation, detection voltage changes can be very fast lots of engineering knowledge Voltage cons: easily affected by environment DC connectivity required? R & C effects slow things down

#### REPRESENTING INFORMATION WITH VOLTAGES

Representation of each point (x, y) in a B&W Picture:

| 0 volts:    | BLACK    |

|-------------|----------|

| I volt:     | WHITE    |

| 0.37 volts: | 37% Gray |

| etc.        | ,        |

Representation of a picture: Scan points in some prescribed raster order... generate voltage waveform

How much information at each point?

#### INFORMATION PROCESSING = COMPUTATION

First, let's consider some processing blocks:

#### LET'S BUILD A SYSTEM!

input

#### output

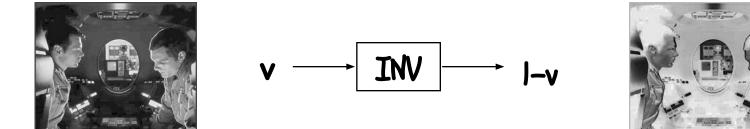

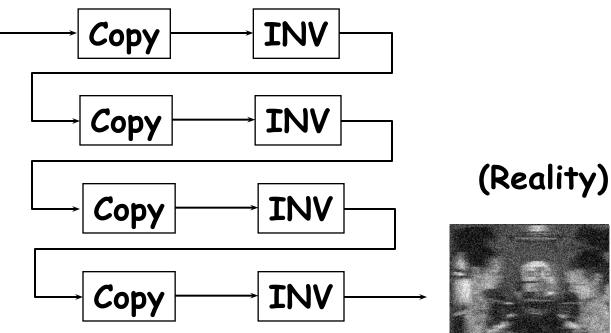

## WHY DID OUR SYSTEM FAIL?

Why doesn't reality match theory?

- 1. COPY Operator doesn't work right

- 2. INVERSION operator doesn't work right

- 3. Theory is imperfect

- Reality is imperfect

Our system architecture stinks {

#### ANSWER: all of the above!

Noise and inaccuracy are inevitable; we can't reliably reproduce infinite information -- we must design our system to tolerate some amount of error if it is to process information reliably.

## THE KEY TO SYSTEM DESIGN

A SYSTEM is a structure that is "guaranteed" to exhibit a specified behavior, assuming all of its components obey their specified behaviors.

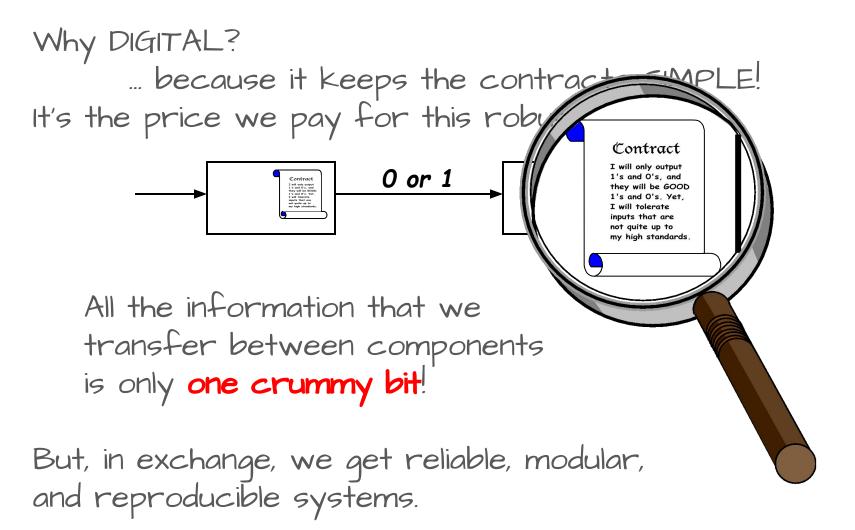

How is this achieved? Through Contracts

Every system component will have clear obligations and responsibilities. If these are maintained we have every right to expect the system to behave as planned. If contracts are violated all bets are off.

### DIGITAL CONTRACTS

10/10/2018

Keep in mind, the real world is not digital, we engineer it to behave that way. We coerce real physical phenomena to implement digital designs!

10/10/2018

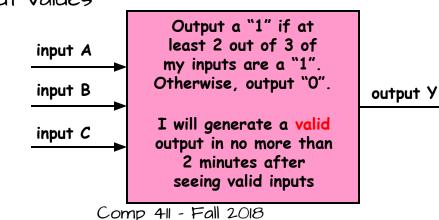

## A DIGITAL PROCESSING ELEMENT

- · A combinational device is a digital element that has

- one or more digital inputs

- one or more digital outputs

- a functional specification that details the value of each output for every possible combination of valid input values

- a timing specification consisting (at a minimum) an upper bound propagation delay, t<sub>pd</sub>, on the required time for the device to compute the specified valid output values from an arbitrary set of stable, valid input values

Static

Discipline

## A COMBINATIONAL DIGITAL SYSTEM

A system of interconnected elements is combinational if

- each circuit element is combinational

- every input is connected to exactly one output or directly to some source of O's or I's

- the circuit contains no directed cycles

#### No feedback (yet!) ~

But, in order to realize digital processing elements we have one more requirement!

#### A definition for a VALID input and a VALID output!

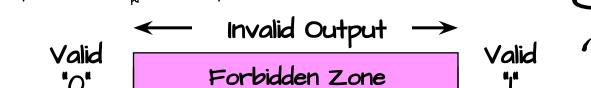

## VALID = NOISE MARGINS

- Key idea:

- Don't allow "O" to be mistaken for a "I" or vice versa

- Use the same "uniform bit-representation convention", for every component in our digital system

- To implement devices with high reliability, we outlaw "close calls" via a representation convention which forbids a range of voltages between "O" and "I".

- Ensure the valid input range is more tolerant (larger) than the valid output range

Our definition of valid does not preclude inputs and outputs from passing through invalid values. In fact, they must, but only during transitions. Our specifications allow for this (i.e. outputs are specified sometime ( $T_{pd}$ ) after after inputs become valid).

volta

10/10/2018

Comp 411 - Fall 2018

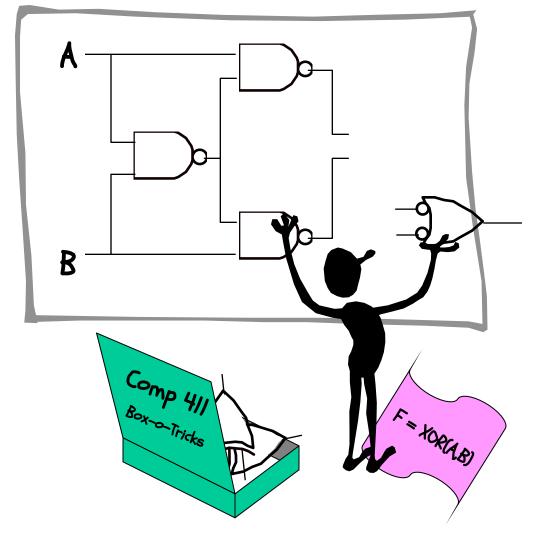

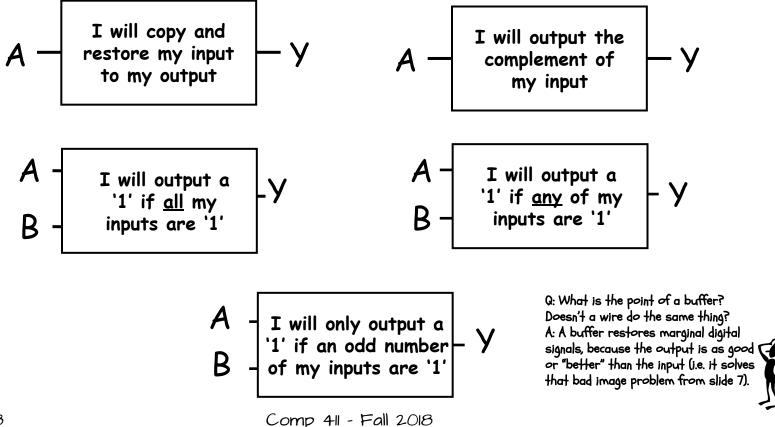

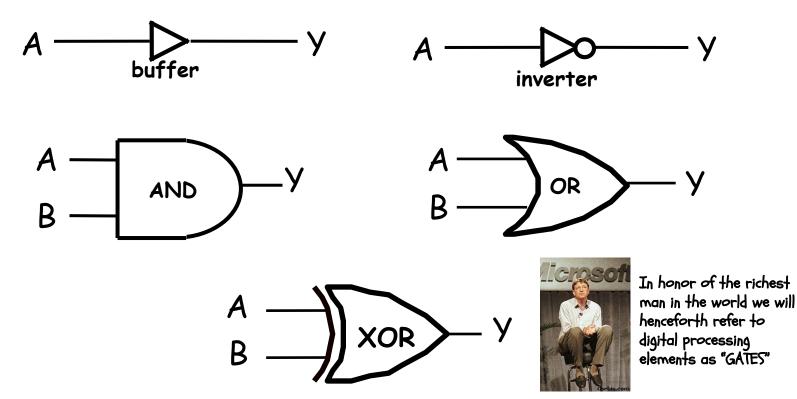

### DIGITAL PROCESSING ELEMENTS

Some digital processing elements occur so frequently that we give them special names and symbols

## DIGITAL PROCESSING ELEMENTS

Some digital processing elements occur so frequently that we give them special names and symbols

10/10/2018

Comp 411 - Fall 2018

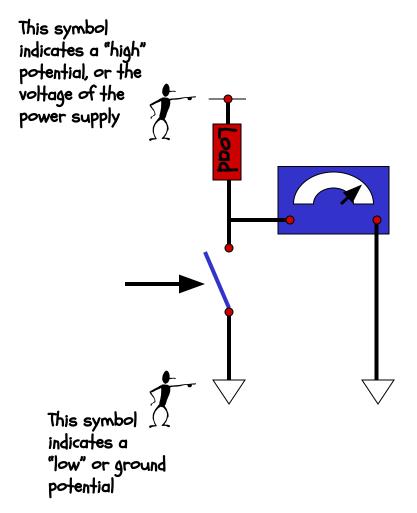

- A controllable switch is the common link of all computing technologies

- How do you control voltages with a switch?

- By creating and opening paths between higher and lower potentials

#### USING TRANSISTORS TO BUILD LOGIC GATES!

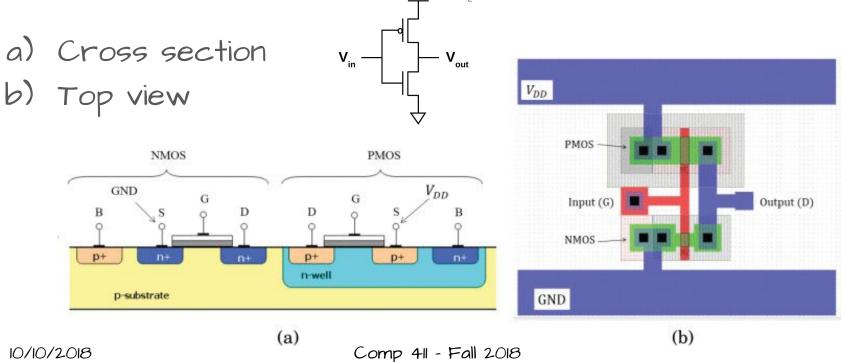

## SCHEMATIC VS. PHYSICAL

These transistors are symbolic or schematic representations of actual devices that are fabricated by etching, diffusing impurties, and masking layers of silicon and metal.

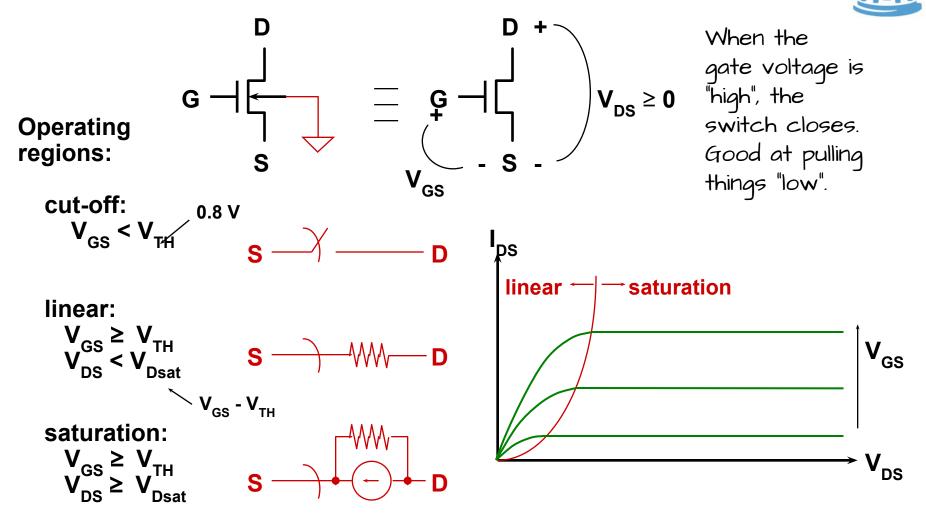

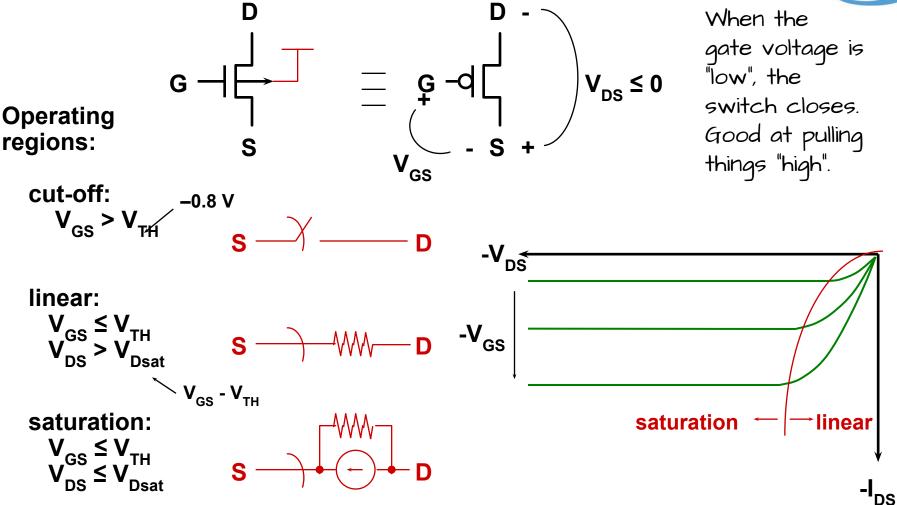

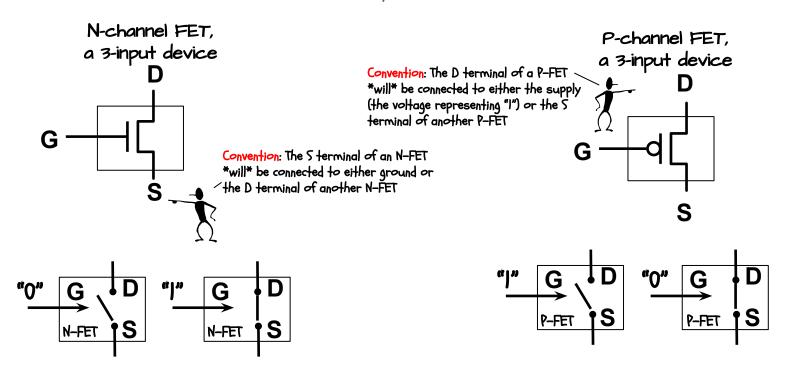

## "DIGITAL" TRANSISTOR ABSTRACTION

- Transistors are extremely flexible, but fickled analog devices.

- If we limit how we use them, (i.e. adopt the following conventions), they can act as robust digital devices.

- Which we can treat as a simple switch abstraction.

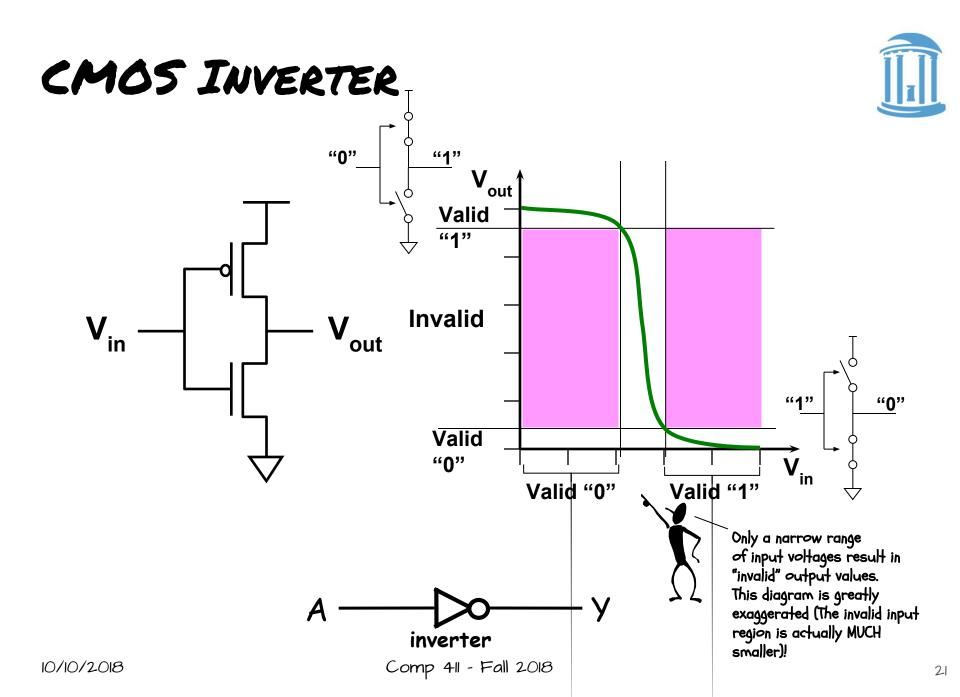

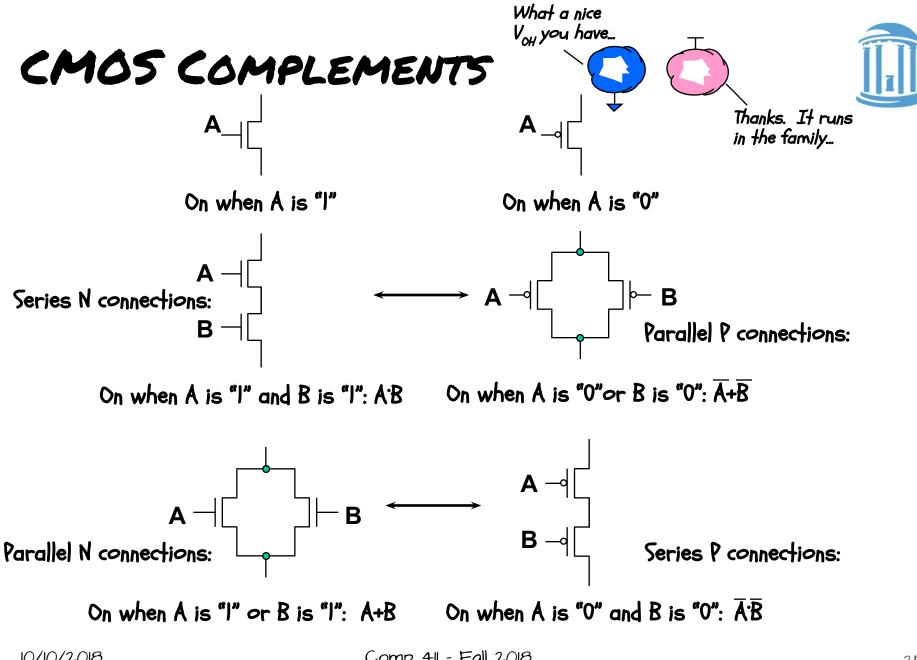

#### COMPLEMENTARY PULLUPS AND PULLDOWNS

This is what the "C" in CMOS stands for!

We design components with *complementary* pullup and pulldown logic (i.e., the pulldown should be "on" when the pullup is "off" and vice versa).

| pullup | pulldown | F(I,,I)                                                        |

|--------|----------|----------------------------------------------------------------|

| on     | off      | driven "1"                                                     |

| off    | on       | driven "O" Convention: In general,<br>/ let's avoid these last |

| on     | on       | driven "X" +wo cases.                                          |

| off    | off      | no connection<br>Strictly following our<br>STATIC DISCIPLINE   |

10/10/2018

(eg. Pass gates and storage devices).

Such devices are only QUASI-DIGITAL!

Comp 411 - Fall 2018

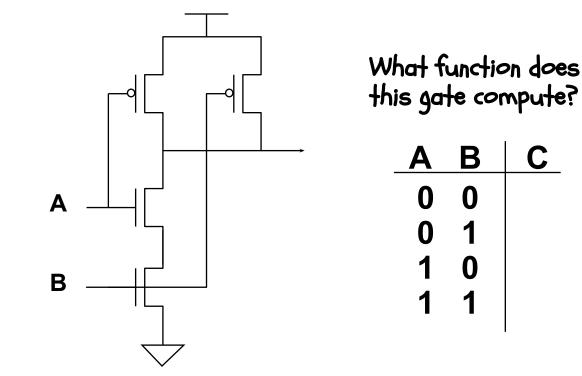

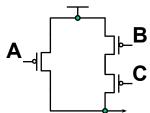

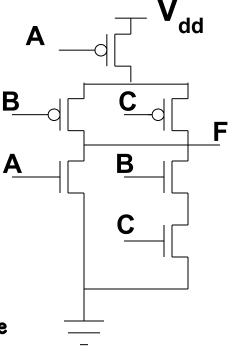

#### A TWO-INPUT LOGIC GATE

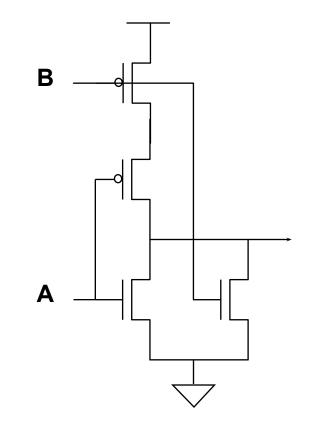

#### HERE'S ANOTHER ...

What function does this gate compute?

| Α | Β | С |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

|   |   |   |

#### 28

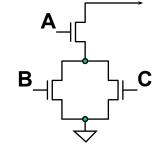

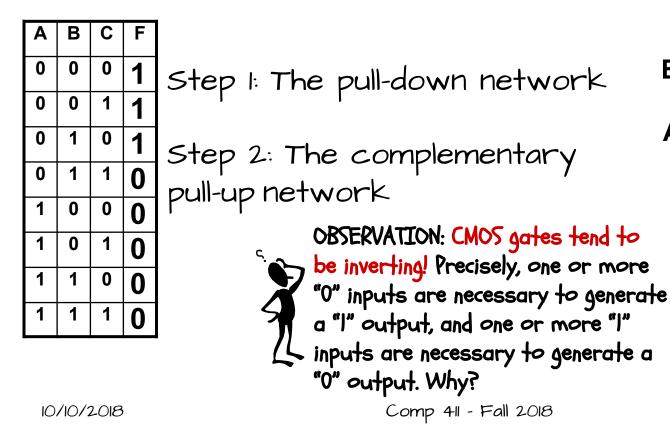

## GENERAL CMOS GATE RECIPE

Step 1. Figure out pulldown network that does what you want (i.e the set of conditions where the output is 'O') e.q., F = A\*(B+C)

Step 2. Walk the hierarchy replacing nfets with pfets, series subnets with parallel subnets, and parallel subnets with series subnets

Step 3. Combine pfet pullup network from Step 2 with nfet pulldown network from Step 1 to form fully-complementary CMOS gate.

### ONE LAST EXERCISE

Let's construct a gate to compute:

$F = \overline{A+BC} = NOT(OR(A,AND(B,C)))$

NEXT TIME

#### Now that we can see what goes on inside of a single gate, we'll next use several them to compose larger systems that compute other logic functions.