#### UNBOUNDED-SPACE COMPUTATION

"science" part of computer science was being developed (long before actual electronic computers existed). Many different "Models of Computation" were proposed, and the classes of "functions" that each could compute were analyzed.

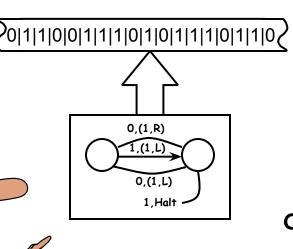

One of these models was the "TURING MACHINE", named after Alan Turing (1912-1954).

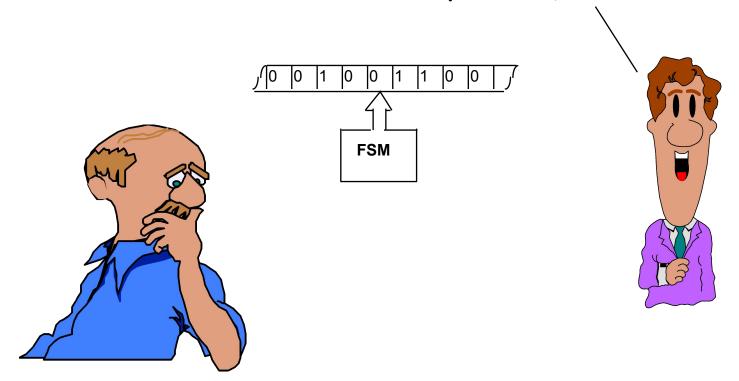

A Turing Machine is just an FSM which receives its inputs and writes outputs onto an "infinite tape". This simple addition overcomes the FSM's limitation that it can only keep track of a "bounded number of events".

## TURING MACHINE TAPES AS INTEGERS

Canonical names for bounded tape configurations:

Note: The FSM part of a Turing Machine is just one of the FSMs in our enumeration. The tape can also be represented as an integer, but this is trickier. It is natural to represent it as a binary fraction, with a binary point just to the left of the starting position. If the binary number is rational, we can alternate bits from each side of the binary point until all that is left is zeros, then we have an integer.

## TMS AS INTEGER FUNCTIONS

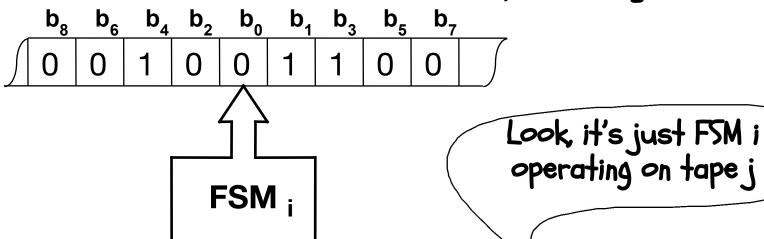

Turing Machine  $T_i$  operating on Tape x, where  $x = ...b_8b_7b_6b_5b_4b_3b_2b_1b_0$

$$y = T_i[x]$$

x: input tape configuration y: output tape when TM halts

I wonder if a TM can compute EVERY integer function...

## ALTERNATIVE MODELS OF COMPUTATION

Turing Machines [Turing]

Hardware head Recursive Functions [Kleene]

$$F(0,x) = x$$

$F(y,0) = y$

$F(y,x) = x + y + F(y-1,x-1)$

(define (fact n)

(... (fact (- n 1)) ...)

Kleene (1909-1994)

Theory

head

Turing

Production Systems [Post, Markov]

Lambda calculus [Church, Curry, Rosser...]

Math head  $\lambda$

λχ.λγ.χχγ

(lambda(x)(lambda(y)(x(xy))))

Church (1903-1995) Turing's PhD Advisor

Post (1897-1954)

# THE 1ST COMPUTER INDUSTRY SHAKEOUT

Here's a TM that computes SQUARE ROOT!

### AND THE BATTLES RAGED

Here's a Lambda Expression that does the same thing...

... and here's one that computes the n<sup>th</sup> root for ANY n!

$$(\lambda(x n) \dots)$$

#### A FUNDAMENTAL RESULT

Turing's amazing proof: Each model is capable of computing exactly the same set of integer functions! None is more powerful than the others.

Proof Technique: Constructions that translate between

models

BIG IDEA: Computability, independent of computation scheme chosen

This means that we know of no mechanisms (including computers) that are more "powerful" than a Turing Machine, in terms of the functions they can compute.

Every discrete function computable by ANY realizable machine is computable by some Turing machine.

## COMPUTABLE FUNCTIONS

The "input" to our computable function will be given on the initial tape, and the "output" will be the contents of the tape when the TM halts.

$$f(x)$$

computable <=> for some k, all x:

$f(x) = T_{k}[x] \equiv f_{k}(x)$

Representation tricks: to compute  $f_k(x,y)$  (2 inputs) <x,y>  $\equiv$  integer whose even bits come from x, and whose odd bits come from y; whence

$$f_K(x, y) \equiv T_K[\langle x, y \rangle]$$

$$f_{12345}(x,y) = x * y$$

$f_{23456}(x) = 1$  iff x is prime, else 0

## TMS, LIKE PROGRAMS, CAN MISBEHAVE |

It is possible that a given Turing Machine may not produce a result for a given input tape. And it may do so by entering an infinite loop!

Consider the given TM.

It scans a tape looking for the first non-zero cell to the right.

What does it do when given a tape that has no is to its left?

We say this TM does not halt for that input!

| Current<br>State | •      | Write<br>Tape |     | Next<br>State |

|------------------|--------|---------------|-----|---------------|

| 50<br>50         | 1<br>0 | 1 0           | L R | Halt<br>50    |

#### ENUMERATION OF COMPUTABLE FUNCTIONS

#### Conceptual table of TM behaviors...

VERTICAL AXIS: Enumeration of TMs. HORIZONTAL AXIS: Enumeration of input tapes. (j ,k) entry = result of  $TM_{\nu}[j]$  -- integer, or \* if it never halts.

Turing Machine Tapes -----

Turing Machine FSMs

|       |                    |                    | 1                  |     |                    |     |

|-------|--------------------|--------------------|--------------------|-----|--------------------|-----|

|       | f <sub>i</sub> (0) | f <sub>i</sub> (1) | f <sub>i</sub> (2) | ••• | f <sub>i</sub> (j) | ••• |

| $f_0$ | <b>※1</b>          | <b>X</b> 3         | <b>X</b> *0        | ••• |                    |     |

| $f_1$ | <b>¾1</b>          | <b>X</b> 0         | <b>866</b>         | ••• |                    |     |

| •••   | •••                | •••                | •••                | ••• | •••                |     |

| $f_k$ | •••                | •••                | •••                | ••• | f <sub>k</sub> (j) |     |

| •••   |                    |                    |                    |     |                    |     |

Every computable function is in this table, since everything that we know how to compute can be computed by a TM.

Do there exist well—specified integer functions that a TM can't compute?

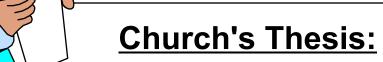

The Halting Problem: Given j. k: Does TMk Halt with input j?

#### THE HALTING PROBLEM

The Halting Function:  $T_H[k, j] = 1$  iff  $TM_k[j]$  halts, else 0 Can a Turing machine compute this function?

Comp 411 - Fall 2017

If T<sub>H</sub> is computable then so is T<sub>Nasty</sub>

# WHAT DOES T NASTY [NASTY] DO?

#### Answer:

$T_{Nasty}[Nasty]$  loops if  $T_{Nasty}[Nasty]$  halts  $T_{Nasty}[Nasty]$  halts if  $T_{Nasty}[Nasty]$  loops

Thus,  $T_H$  is not computable by a Turing Machine!

11/6/2017

### LIMITS OF TURING MACHINES

A Turing machine is formal abstraction that addresses

- · Fundamental Limits of Computability -

- What is means to compute.

- The existence of uncomputable functions.

- · We know of no machine more powerful than a Turing machine in terms of the functions that it can compute.

#### But they ignore

- · Practical coding of programs

- · Performance

- · Implementability

- · Programmability

- ... these latter issues are the primary focus of contemporary computer science (Remainder of Comp 411)

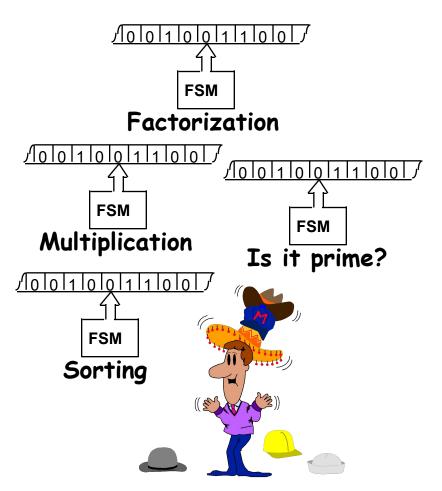

## COMPUTABILITY VS. PROGRAMMABILITY

Recall Church's thesis:

"Any discrete function computable by ANY realizable machine is computable by some Turing Machine"

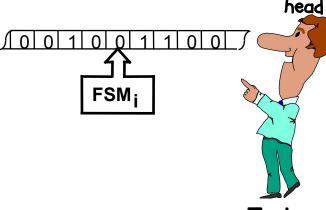

We've defined what it means to COMPUTE (whatever a TM can compute), but, a Turing machine is nothing more that an FSM that receives inputs from, and outputs onto, an infinite tape.

So far, we've been designing a new FSM for each new Turing machine that we encounter.

Wouldn't it be nice if we could design a more general-purpose Turing machine?

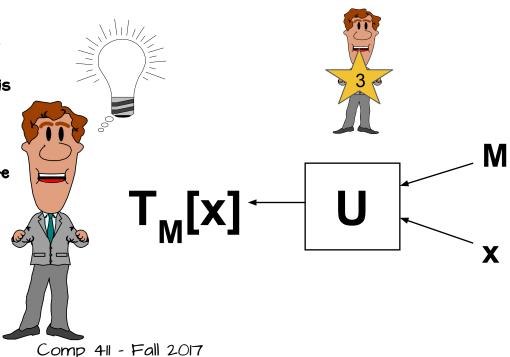

#### PROGRAMS AS DATA

What if we encoded the description of the FSM on our tape, and then wrote a general purpose FSM to read the tape and EMULATE the behavior of the encoded machine? We could just store the state-transition table for our TM on the tape and then design a new TM that makes reference to it as often as it likes. It seems possible that such a machine could be built.

"It is possible to invent a single machine which can be used to compute any computable sequence. If this machine U is supplied with a tape on the beginning of which is written the S.D. ["standard description" of an action table] of some computing machine M, then U will compute the same sequence as M."

- Turing 1936 (Proc of the London Mathematical Society, Ser. 2, Vol. 42)

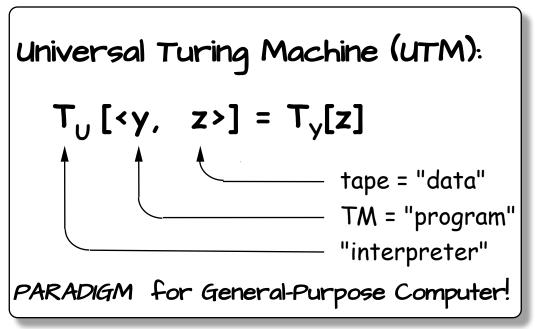

## FUNDAMENTAL RESULT: UNIVERSALITY

Define "Universal Function":  $U(x,y) = T_x(y)$  for every x, y ... Surprise! U(x,y) IS COMPUTABLE, hence  $U(x,y) = T_u(\langle x,y \rangle)$  for some  $U(x,y) = T_u(\langle x,y \rangle)$

INFINITELY many UTMs ...

Any one of them can evaluate any computable function by simulating/emulating/interpreting the actions of Turing machine given to it as an input.

#### **UNIVERSALITY:**

Basic requirement for a general purpose computer

#### DEMONSTRATING UNIVERSALITY

Complete,

Suppose you've designed Turing Machine  $T_k$  and want to show that its universal.

#### APPROACH:

- 1. Find some known universal machine, say  $T_{u}$ .

- 2. Devise a program, P, to simulate  $T_u$  on  $T_k$ :  $T_k[\langle P, x \rangle] = T_u[x] \text{ for all } x.$

3. Since  $T_{ij}[\langle y,z\rangle] = T_{ij}[z]$ , it follows that, for all y and z.

$$T_K[\langle P, \langle y, z \rangle \rangle] = T_U[\langle y, z \rangle] = T_U[z]$$

CONCLUSION: Armed with program P, machine Tk can mimic the behavior of an arbitrary machine  $T_{\nu}$  operating on an arbitrary input tape z.

**HENCE**  $T_k$  can compute any function that can be computed by any Turing Machine.

#### NEXT TIME

Enough theory already, let's build something!

#### BUILDING A COMPUTER

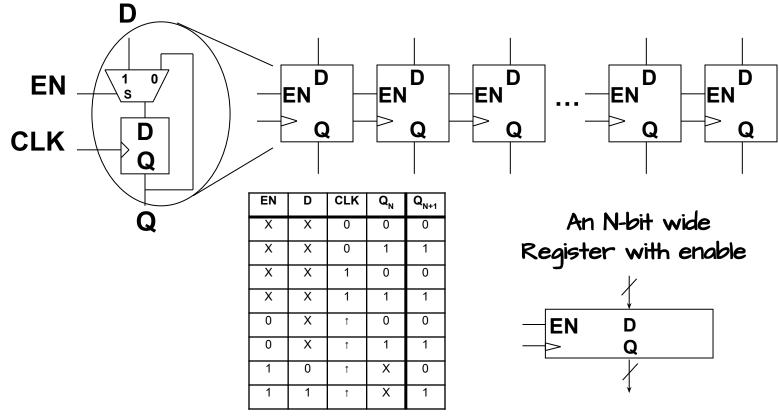

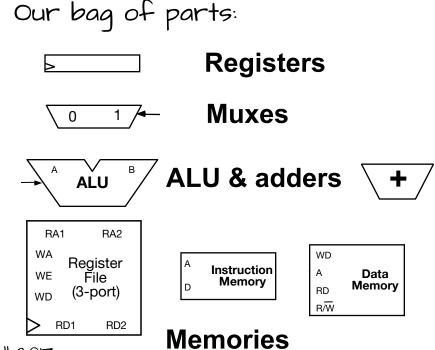

#### ANOTHER FUNCTIONAL UNITS

We'll need functional units fast memories. We begin by building "wide" registers. First, we'll add a control that "enables" the loading of a register.

11/6/2017

Comp 411 - Fall 2017

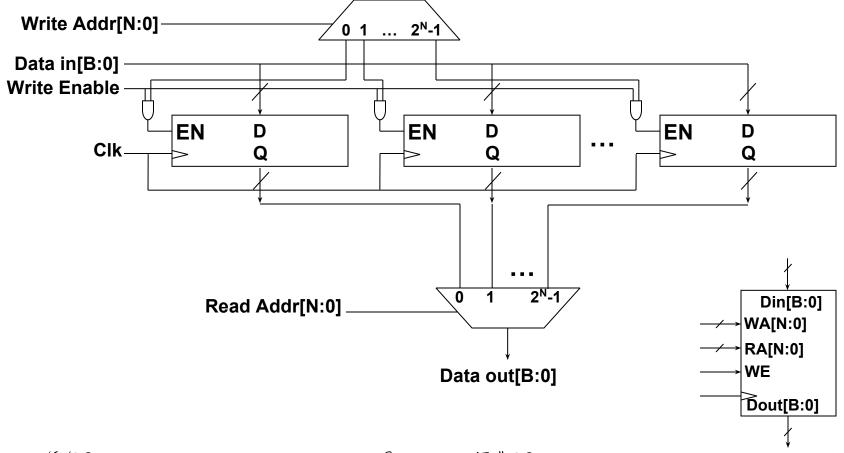

## A REGISTER FILE

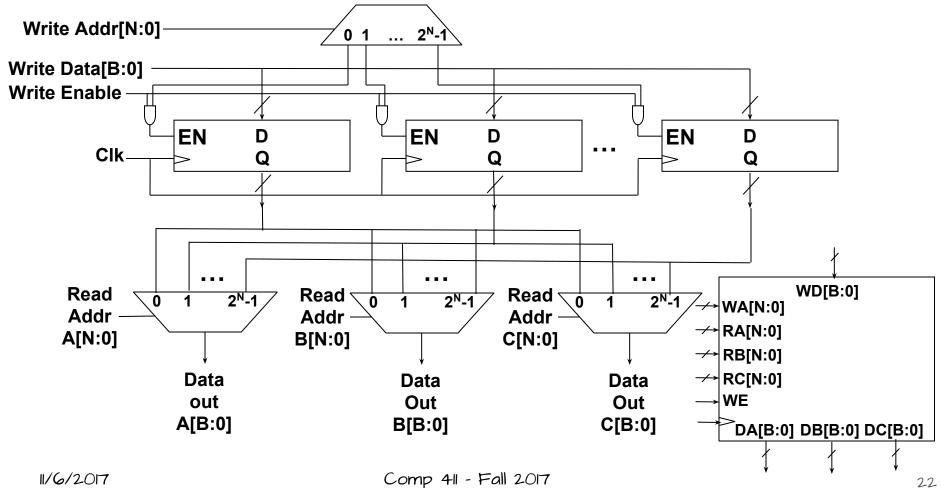

We can also construct an addressable array of registers

## A MULTI-PORTED REGISTER FILE

We can add multiple read ports by simply adding more output MUXs

Comp 411 - Fall 2017

### THIS 15 17!

This is where our story actually begins. We are now ready to build a computer.

The ingredients are all in place. It is time to build a legitimate computer. One that executes instructions, much the way any desktop, tablet, smartphone, or other computer does.

#### THE ARMY ISA

|         | 4                   | 3   | 4        | 1        | 4  | 4  | 5         | 2 1    | 4   |

|---------|---------------------|-----|----------|----------|----|----|-----------|--------|-----|

| R type: | Cond                | 000 | Opcode S |          | Rn | Rd | Shift     | L<br>A | Rm  |

|         | 4                   | 3   | 4        | 4 1      |    | 4  | 4 8       |        | 8   |

| I type: | Cond                | 001 | Opcode   | Opcode S |    | Rd | Shift Imm |        | lmm |

|         | 4                   | 3   | 5        |          | 4  | 4  | 12        |        |     |

| D type: | Cond                | 010 | AddrMod  | AddrMode |    | Rd | lmm12     |        |     |

|         | 4                   | 3   | 5        | 5        |    | 4  | 5         | 2 1    | 4   |

| X type: | Cond                | 011 | AddrMod  | AddrMode |    | Rd | Shift     | L O    | Rm  |

|         | 4                   | 3   | 1        | 1 24     |    |    |           |        |     |

| B type: | e: Cond 101 L Imm24 |     |          |          |    |    |           |        |     |

#### Five key instruction formats: 0) ALU with two register operands

- 1) ALU with a register and an immediate operand

- 2) Load/Store with an immediate offset

- 3) Load/Store with a register offset

- 5) Branch

#### DESIGN APPROACH

#### Incremental Featurism:

Each instruction class can be implemented using our component repertoire. We'll try implementing data paths for each class individually, and merge them as we go (using Muxes, etc).

#### Steps:

- 1. 3-Operand ALU instructions

- 2. ALU w/immediate instructions

- 2. Load & Store Instructions

- 3. Branch instructions

- 4. Leftovers

- 5. Reset & Exceptions

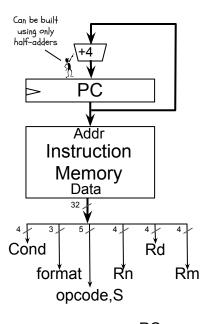

#### INSTRUCTION FETCH/DECODE

• Fetch an instruction, and decode it

- use PC as memory address

- add 4 to current PC, and update PC on the next rising clock

- fetch instruction from memory

- We'll use some instruction ' fields directly (register numbers, constants)

- use format, opcode bits, and a few assorted bits to generate

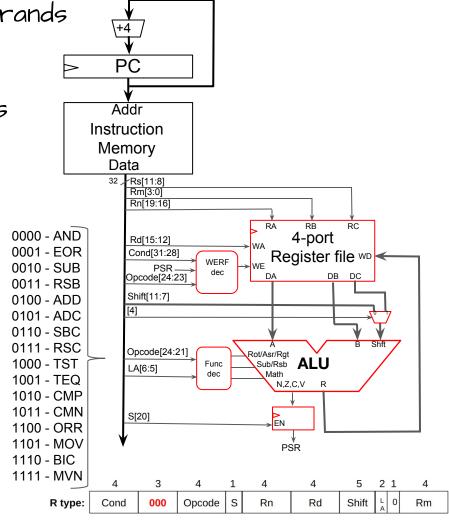

## R-TYPE DATA PROCESSING

ALU instructions with register operands

Rd - register file write address Rn, Rm - register source operands Shift or Rs - Optional shift of Rm

LA - direction and type of shift

S-bit - controls update of PSR

Func decoding from ALU lecture

Register write back controlled

by WERF logic

WERF!

## NEXT TIME

More instructions...

Comp 411 - Fall 2017

#### WERF LOGIC

Not every instruction updates a destination register

CMP, CMN, TST, TEQ don't update any register

Conditional execution is controlled by the WERF logic. WE is set only if the condition is met. Otherwise it is effectively annulled...

| I <sub>31</sub> | I <sub>30</sub> | l <sub>29</sub> | I <sub>28</sub> | l <sub>24</sub> | l <sub>23</sub> | WE           | Notes           |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------|-----------------|

| Х               | Х               | Х               | Х               | 1               | 0               | 0            | cmp,cmn,tst,teq |

| 1               | 1               | 1               | 0               | 0               | Х               | 1            | Cond = AL       |

| 1               | 1               | 1               | 0               | Х               | 1               | 1            | Cond = AL       |

| 0               | 0               | 0               | 0               | 0               | Х               | Z            | Cond = EQ       |

| 0               | 0               | 0               | 0               | Х               | 1               | Z            | Cond = EQ       |

| 0               | 0               | 0               | 1               | 0               | Х               | !Z           | Cond = NE       |

| 0               | 0               | 0               | 1               | Х               | 1               | !Z           | Cond = NE       |

|                 |                 |                 |                 |                 |                 |              |                 |

| 1               | 1               | 0               | 0               | 0               | Х               | !(Z   (N^V)) | Cond = GT       |

| 1               | 1               | 0               | 0               | Х               | 1               | !(Z   (N^V)) | Cond = GT       |

| 1               | 1               | 0               | 1               | 0               | Х               | Z   (N^V)    | Cond = LE       |

| 1               | 1               | 0               | 1               | Х               | 1               | Z   (N^V)    | Cond = LE       |