### STATUS FLAGS

Now it is time to discuss what **status flags** are available. These five status flags are kept in a special register called the Program Status Register (PSR). The PSR also contains other important bits that control the processor.

- N set if the result of an operation is negative (Most Significant Bit (MSB) is a 1)

- Z set if the result of an operation is "O"

- C set if the result of an operation has a carry out of it's MSB

- V set if a sum of two positive operands gives a negative result, or if the sum of two negative operands gives a positive result

- Q a sticky version of overflow created by instructions that generate multiple results (more on this later on).

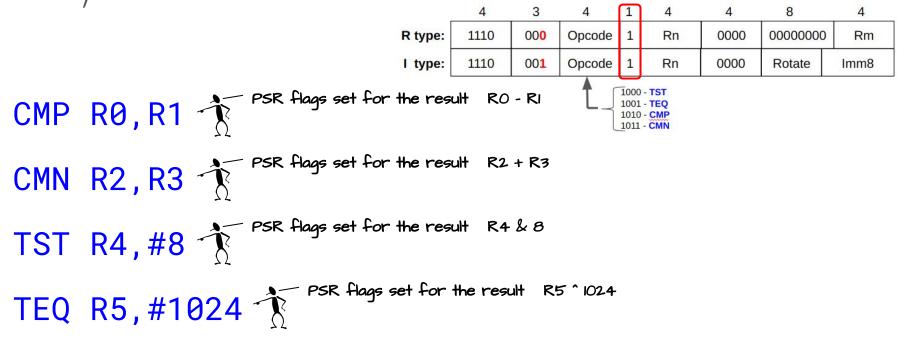

### COMPARISON INSTRUCTIONS

These instructions modify the status flags, but leave the contents of the registers unchanged. They are used to test register contents, and they **must** have their "S" bit set to "I". They also don't modify their Rd, and by **convention**, Rd is set to "0000".

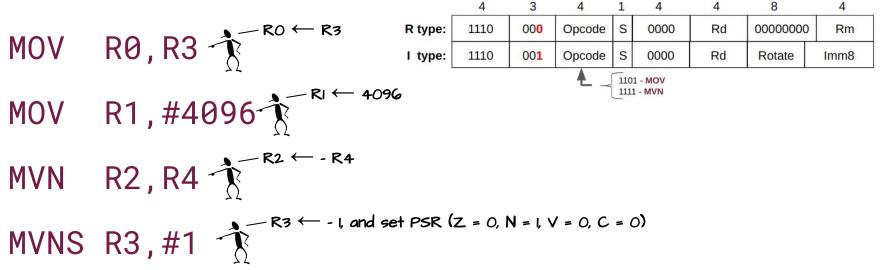

#### REGISTER TRANSFER

These instructions are used to transfer the contents of one register to another, or simply to initialize the contents of a register. They make use of only one operand, and, by convention, have their Rn field set to "0000".

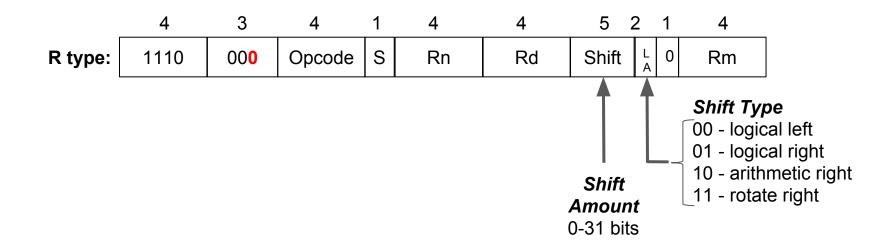

## ARM SHIFT OPERATIONS

A novel feature of ARM is that **all** data-processing instructions can include an optional "shift", whereas most other architectures have separate shift instructions. This is actually very useful as we will see later on. The key to shifting is that 8-bit field between Rd and Rm.

#### 09/13/2017

# Left Shifts effectively multiply the contents of a register by 2<sup>s</sup> where s is the shift amount.

#### MOV R0, R0, LSL 7

LEFT SHIFTS

| R0 be | efore: | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0111 | = 7                        |

|-------|--------|------|------|------|------|------|------|------|------|----------------------------|

| R0 a  | after: | 0000 | 0000 | 0000 | 0000 | 0000 | 0011 | 1000 | 0000 | = 7 * 2 <sup>7</sup> = 896 |

Shifts can also be applied to the second operand of any data processing instruction

#### ADD R1, R1, R0, LSL 7

### RIGHT SHIFTS

Right Shifts behave like *dividing* the contents of a register by 2<sup>s</sup> where s is the shift amount, *if* you assume the contents of the register are *unsigned*.

#### MOV R0, R0, LSR 2

| R0 before: | 0000              | 0000 | 0000 | 0000 | 0000 | 0100 | 0000 | 0000 | = 1024                        |

|------------|-------------------|------|------|------|------|------|------|------|-------------------------------|

| R0 after:  | <mark>0000</mark> | 0000 | 0000 | 0000 | 0000 | 0001 | 0000 | 0000 | = 1024 / 2 <sup>2</sup> = 256 |

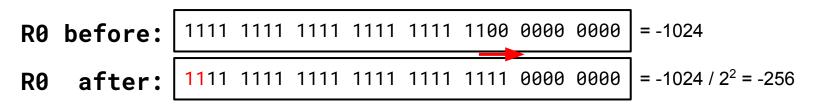

## ARITHMETIC RIGHT SHIFTS

Arithmetic right shifts behave like *dividing* the contents of a register by 2<sup>s</sup> where s is the shift amount, *if* you assume the contents of the register are *signed*.

#### MOV R0, R0, ASR 2

This is Java's ">>>" operator, LSR is ">>" and LSL is "<<"

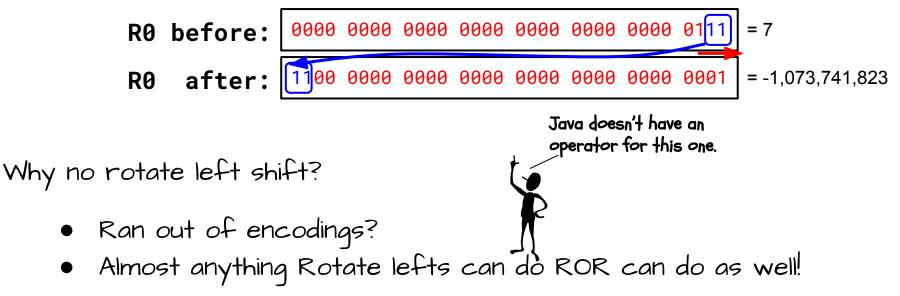

## ROTATE RIGHT SHIFTS

Rotating shifts have no arithmetic analogy. However, they don't lose bits like both logical and arithmetic shifts. We saw rotate right shift used for the I-type "immediate" value earlier.

#### MOV RØ, RØ, ROR 2

### ADDRESSING MODES AND BRANCHES

- More on Immediates

- Reading and Writing Memory

- Registers holding addresses

- Pointers

- Changing the PC

- Loops

- Labels

- Calling Functions

#### WHY BUILT-IN CONSTANT OPERANDS? (IMMEDIATES)

|         | 4    | 3   | 4      | 1 | 4  | 4  | 4      | 8    |

|---------|------|-----|--------|---|----|----|--------|------|

| I type: | 1110 | 001 | Opcode | S | Rn | Rd | Rotate | lmm8 |

Alternatives? Why not? Do we have a choice?

o put constants in memory (was common in older instruction sets)

- SMALL constants are used frequently (50% of operands)

In a C compiler (gcc) 52% of ALU operations involve a constant

In a circuit simulator (spice) 69% involve constants

e.g., B = B + 1; C = W & 0xff; A = B 1;

- ISA Design Principle:

Make the common case easy

Make the common case fast

How large of constants should we allow for? If they are too big, we won't have enough bits leftover for the instructions or operands.

Ш

8

imm

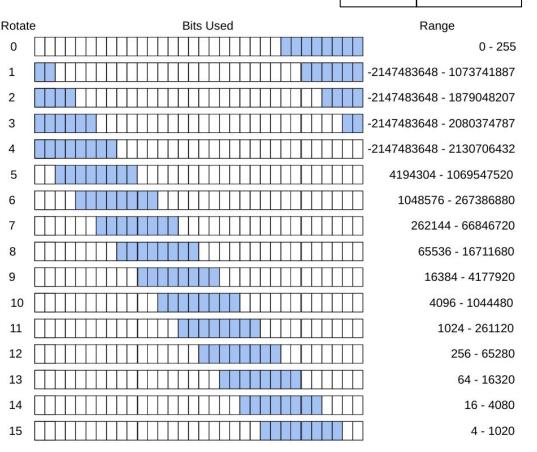

## ROTATIONS TO MAKE CONSTANTS

Recall that immediate constants are encoded in two parts: Thus, only a subset of 4096 32-bit numbers can Rotate

be used directly as an operand.

There are actually only **3073** distinct constants. There are 16, "Os" and 4 ways to represent all powers 2.

From last time, how might you encode 256? [1100 00000001] [1101 00000100] [1110 00010000] [1111 01000000] 09/13/2017

#### MOVES AND ORS

We can load any 32-bit constant using a series of instructions, one-byte at a time.

| MOV R0,#85            | ; 0x55 in hex       |

|-----------------------|---------------------|

| ORR R0,R0,#21760      | ; 0x5500 in hex     |

| ORR R0,R0,#5570560    | ; 0x550000 in hex   |

| ORR R0,R0,#1426063360 | ; 0x55000000 in hex |

But there are often better, faster, ways to load constants, and the assembler can figure out how for you, even if it needs to generate multiple instructions.

MOV R0, =1431655765 ; 0x55555555 in hex Note that an equal sign is used here rather than a hashtag.

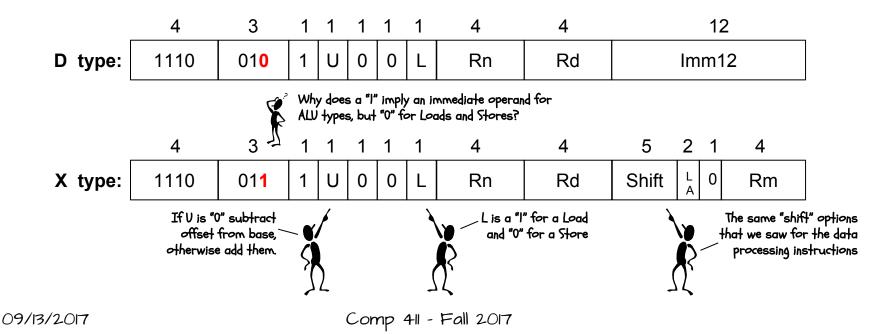

## LOAD AND STORE INSTRUCTIONS

ARM is a "Load/Store architecture". That means that only a special class of instructions are used to reference data in memory. As a rule, data is loaded into registers first, then processed, and the results are written back using stores. Load and Store instructions have their own format:

## LOAD AND STORE OPTIONS

ARM's load and store instructions are versatile. They provide a wide range of addressing modes. Only a subset is shown here.

LDR Rd, [Rn, #imm12]  $\Re$  Rd  $\leftarrow$  Memory[Rn + imm12] Rd is loaded with the contents of memory at the address found by adding the contents of the base register to the supplied constant

STR R0, [R1, #-4]

$$\bigwedge$$

Memory[RI - 4]  $\leftarrow$  R0

Offsets can be either added or subtracted as indicated by a negative sign

LDR R2, [R3]  $\bigwedge$  If no offset is specified it is assumed to be zero

STR R4, [R5, R6]  $\bigwedge$  The contents of a second register can be used as an

offset rather than a constant (using the X-type format)

LDR R4, [R5, -R6]  $\bigwedge$  Register offsets can be either added or subtracted like

constants

STR R4, [R5, R4, LSL 2]  $\bigwedge$  Register offsets can also be optionally shifted which is

great for indexing arrays!

09/13/2017

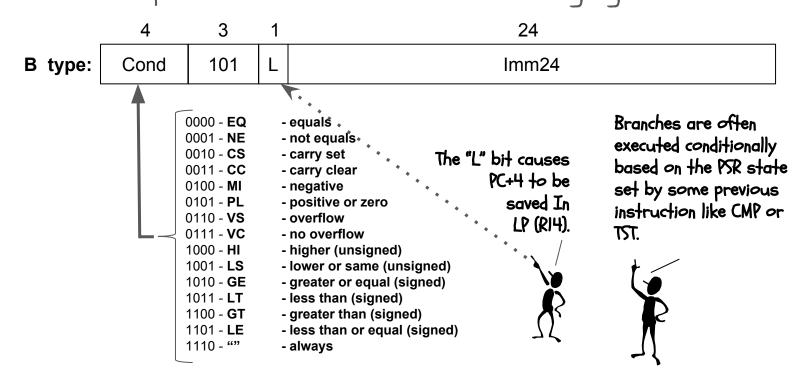

#### CHANGING THE PC

The Program Counter is special register (R15) that tracks the address of the next instruction to be fetched. There are special instructions for changing the PC.

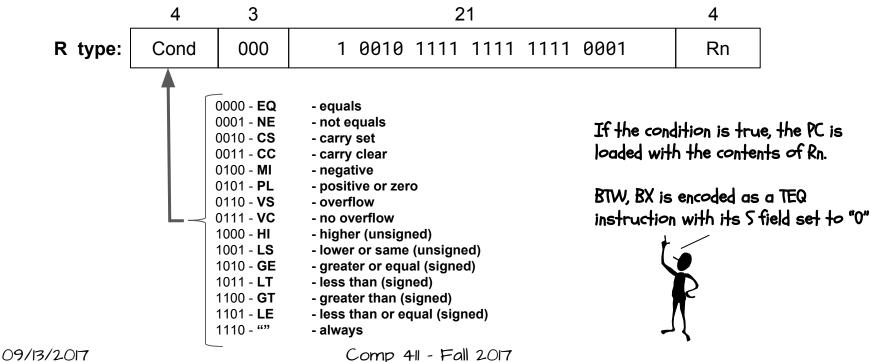

## BRANCH USING REGISTERS

The standard Branch instruction has a limited range, the 24-bit signed 2's complement immediate value is multiplied by 4 and added to the PC+8, giving a range of +/- 32 Mbytes. Larger branches make use of addresses previously loaded into a register using the BX instruction.

16

#### BRANCH EXAMPLES

BNE else *if some previous CMP instruction had a non-zero result (i.e. making the "Z" bit 0 in the PSR), then this instruction will cause the PC to be loaded with the address having the label "else".* If some previous CMP instruction set the "Z" bit in the PSR, then this instruction will cause the PC to be loaded with the address having the label "func", and the address of the following instruction will be saved BEQL func

in R14.

Loads the PC with the contents of R14. BX LR

loop: B loop An infinite loop

#### A SIMPLE PROGRAM

- ; Assembly code for

- sum = 0;

- for (i = 0; i <= 10; i++)

- sum = sum + i;

- MOV R1,#0 MOV R0,#0 loop: ADD

- ADD R1,R1,#1 ; i++ R1,#10 CMP

- BLE loop

- halt: B halt

- ; R1 is i ; R0 is sum

- R0,R0,R1 ; sum = sum + i

- ; i <= 10

#### LOAD AND STORES IN ACTION

An example of how loads and stores are used to access arrays.

Java/C:

int x[10];

int cum = 0

```

int sum = 0;

```

```

for (int i = 0; i < 10; i++)

sum += x[i];</pre>

```

Assembly:

| .align | 4                                                                                                                                                          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x:     | .space 40                                                                                                                                                  |

| sum:   | .word 0                                                                                                                                                    |

| for:   | <pre>MOV R0,=x ; base of x MOV R1,=sum LDR R2,[R1] MOV R3,#0 ; R3 is i LDR R4,[R0,R3 LSL 2] ADD R2,R2,R4 ADD R3,R3,#1 CMP R3,#10 BLT for STR R2,[R1]</pre> |

#### 09/13/2017

#### 20

We'll write more Assembly programs

Still some loose ends

NEXT TIME

• Multiplication? Division? Floating point?