#### Addressing Modes and Other ISAs

- Where is the data?

- Addresses as data

- Names and Values

- Indirection

### Assembly Exercise

- Let's write some assembly language programs

- Program #1: Write a function "isodd(int X)" which returns

1 if it's argument "X" is odd and O otherwise

| main:<br>halt: | addiu<br>jal<br>addiu<br>jal<br>beq | \$a0,\$0,37<br>isodd<br>\$a0,\$0,42<br>isodd<br>\$0,\$0,halt | The addiu instruction is<br>used to load constants<br>(i.e. isodd(37)), can this<br>be done in other ways? |

|----------------|-------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| isodd:         | andi                                | \$∨0,\$a0,1                                                  | The function is                                                                                            |

|                | jr                                  | \$31                                                         | implemented using only                                                                                     |

implemented using only one instruction. How does "andi \$Y,\$X,1" determine that \$X is odd?

### Your Turn

Program #2: A function "ones(int X)" that returns a count of the number of ones in its argument "X"

#### The MIPS ISA

32-bit (4-byte) ADD instruction:

op = R-type Rs Rt Rd func = add

Means, to MIPS, Reg[3] = Reg[4] + Reg[2]

But, most of us would prefer to write add \$3, \$4, \$2 (ASSEMBLER) or, better yet, a = b + c; (C)

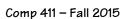

- Once, 1974, there was an heroic effort to build a single -chip computer on a budget of 3500 devices, by a Silicon Valley startup called Intel, that could sell for < \$200.</li>

- It had one primary 8-bit register, A, for accumulator, and

6 other 8-bit registers, B, C, D, E, H, and L with more limited and special functions. Certain register pairs could be linked to act as 16-bit registers, BC, DE, and

HL, mostly for addressing 65536 bytes of memory.

It had one other register, SP, which was always

16-bits and was used to implement a stack.

| - |                 |       |                   |

|---|-----------------|-------|-------------------|

|   | A (accumulator) | Flags | The second second |

|   | В               | С     | 24                |

|   | D               | E     |                   |

| ſ | н               | L     |                   |

|   | SP              |       |                   |

• Typical instructions

| ADD s | A 🗲 A + s |

|-------|-----------|

| SUB s | A 🗲 A – s |

| ANA s | A 🗲 A & s |

|       |           |

ORA s

CMP s

- XRA s

- $A \leftarrow A \mid s \checkmark$  $A \leftarrow A \land s$  $A \leftarrow S \land s$  $A s \qquad \text{Note: Sets}_{\text{flags only}}$

- INR d  $d \leftarrow d+1$

- DCR d  $d \leftarrow d 1$

- A really cool one:

MOV d, s  $d \leftarrow s$

#### where d, s one of {A,B,C,D,E,H,L,Mem[HL]}

Notice how most instructions include only one operand d or s. This is possible, because the other operand and the destination are implicit. They are either both the accumulator, A, or the operand specifies both source and destination and the other operand is a constant. Instructions with one operand are called one-address machines.

| A (accumulator) | Flags |  |

|-----------------|-------|--|

| В               | С     |  |

| D               | E     |  |

| н               | L     |  |

| SP              |       |  |

- Immediate Operands

- ADI  $imm_{\partial}$ A  $\leftarrow$  A +  $imm_{\partial}$ SUI  $imm_{\partial}$ A  $\leftarrow$  A  $imm_{\partial}$ ANI  $imm_{\partial}$ A  $\leftarrow$  A &  $imm_{\partial}$ ORI  $imm_{\partial}$ A  $\leftarrow$  A |  $imm_{\partial}$ XRI  $imm_{\partial}$ A  $\leftarrow$  A ^  $imm_{\partial}$ CPI  $imm_{\partial}$ A  $imm_{\partial}$ MVI d,  $imm_{\partial}$ d  $\leftarrow$   $imm_{\partial}$

- Register Pair Operands INX p  $p \leftarrow p+1$ DCX p  $p \leftarrow p-1$ DAD p HL \leftarrow HL + p LXI p,imm<sub>16</sub>  $p \leftarrow imm_{16}$ where p is one of {BC, DE, HL, or SP}

| A (accumulator) | Flags |  |

|-----------------|-------|--|

| В               | С     |  |

| D               | E     |  |

| н               | L     |  |

| SP              |       |  |

No operands

| RAL  | a 🗲 a << 1 |

|------|------------|

| RAR  | a 🗲 a >> 1 |

| XCHG | HL ←→ DE   |

• Fancy Memory Reference (recall s and d can be Mem[HL])

| LDA addr <sub>16</sub>  | A ← Mem[             | addr <sub>16</sub> ]   |                        |  |  |

|-------------------------|----------------------|------------------------|------------------------|--|--|

| STA addr <sub>16</sub>  | $A \rightarrow Mem[$ | addr <sub>16</sub> ]   |                        |  |  |

| LHLD addr <sub>16</sub> | HL 🗲 Men             | 1[addr <sub>16</sub> ] |                        |  |  |

| SHLD addr <sub>16</sub> | HL $\rightarrow$ Mem | 1[addr <sub>16</sub> ] |                        |  |  |

| LDAX p                  | A ← Mem[             | [p] (p is              | (p is one of {BC, DE}) |  |  |

| STAX p                  | $A \rightarrow Mem[$ | [p]                    |                        |  |  |

| XTHL                    | HL ←→ M              | em[SP]                 |                        |  |  |

| in the following p is a | one of               | [                      |                        |  |  |

| {A   flags, BC, DE, or  |                      | A (accumulator)        | Flags                  |  |  |

|                         | 1165                 | 12                     | C                      |  |  |

PUSH p Mem[SP-1]  $\leftarrow p_L$ ; Mem[SP-2]  $\leftarrow p_H$ ; SP  $\leftarrow$  SP -2

POP p  $p_H \leftarrow Mem[SP];$   $p_L \leftarrow Mem[SP+1];$  $SP \leftarrow SP + 2$

|   | A (accumulator) | Flags |  |

|---|-----------------|-------|--|

| • | В               | С     |  |

|   | D E             |       |  |

|   | Н               | L     |  |

|   | SP              |       |  |

- Branch and control

- JMP addr<sub>16</sub> JNZ addr<sub>16</sub> JZ addr<sub>16</sub> JNC addr<sub>16</sub> JC addr<sub>16</sub>

$PC \leftarrow Mem[addr_{16}]$ if Flags.Z = 0 PC \leftarrow Mem[addr\_{16}] if Flags.Z = 1 PC \leftarrow Mem[addr\_{16}] if Flags.C = 0 PC \leftarrow Mem[addr\_{16}] if Flags.C = 1 PC \leftarrow Mem[addr\_{16}]

CALL addr<sub>16</sub> CNZ addr<sub>16</sub> CZ addr<sub>16</sub> CNC addr<sub>16</sub> CC addr<sub>16</sub> CALL instructions behave similar to their corresponding JMP instructions. However, they also do the following: MEM[SP] ← PC; SP ← SP -2

| A (accumulator) | Flags |  |

|-----------------|-------|--|

| В               | С     |  |

| D               | E     |  |

| н               | L     |  |

| SP              |       |  |

## Growing to a Two-Address Machine

- Intel's 8080 was a huge success, but it soon started to exhibit growing pains that limited its usefulness in comparison to *minicomputers* of the same era.

- Key Problems:

- 8-bit registers were too small

- The maximum of addressable 65536 bytes was too limiting

- So it grew into the 8086, 16-bit architecture (1978)

### Growing to a Two-Address Machine

- This change came with more innovations

- Assembly-language/mnemonic compatibility

- Making the AX, BX, CX, and DX more general purpose (i.e. all could be used like accumulators)

- Similar, but different two-operand instructions:

I am intentionally ignoring lots of crazy instructions like "AAA- Add with an ASCII Adjust," for adding digits encoded in ASCII

| $d \leftarrow d + s$                          |

|-----------------------------------------------|

| d←d-s 👔                                       |

| d←d&s ∬                                       |

| d 🗲 d I s                                     |

| d 🗲 d ^ s                                     |

| d <del>( s</del>                              |

| (,imm <sub>16</sub> ,sext(Imm <sub>8</sub> ), |

| <sub>6</sub> ], Mem[SI],                      |

|                                               |

Mem[SI+addr<sub>16</sub>], Mem[BP+SI]} d is {AX,BX,CX,DX, Mem[addr<sub>16</sub>], Mem[DI], Mem[DI+addr<sub>16</sub>], Mem[BP+DI]}

#### Growing to a Two-Address Machine

- There was one more major addition

- 4 segment registers extend addresses to 20-bits (1048576 bytes)

- Technically, addresses are to any of 65536 bytes offset from a 16-byte aligned segment

Mem[X] = Mem[((segment register) < <4) + X] where the segment

register varies depending

on the "type" of access.

Memory accesses for instructions (involving the PC) use CS (code segment), for data use DS (data segment) or ES (extra segment), and for stack operations (involving SP) use SS (stack segment)

| CS |

|----|

| DS |

| 66 |

| ES |

Comp 411 - Fall 2015

## More Growing Pains (x86)

- Once again the 8088, 8086, 80186, and 80286 machines were immensely successful (IBM PC, Compaq, Clones), and, once again, they started to show limitations compared to a new class of machines called workstations.

- Intel introduced the i386 and i486 extensions

- Registers expanded to 32-bits

- Address space non-segmented,

"flat" 4,294,967,296 bytes

- Segment registers

- Not extended to 32-bits. Two new ones are added.

- Segmented addressing is deemphasized aside from backward compatibility

- Take on more general-purpose roles as scaled offsets (eg. Mem[SI+(DS<<4)])</li>

| 31 16 | 15 | 8 <sub>1</sub> 7 |    | 0 |

|-------|----|------------------|----|---|

| EAX   | AH | AX               | AL |   |

| EBX   | ВН | ВΧ               | BL |   |

| ECX   | СН | СХ               | CL |   |

| EDX   | DH | DX               | DL |   |

| ESP   |    | SP               |    |   |

| EBP   |    | BP               |    |   |

| ESI   |    | ୨୲               |    |   |

| EDI   |    | DI               |    |   |

|       |    |                  |    |   |

| DI |

|----|

| CS |

| D6 |

| 55 |

| ES |

| FS |

| GS |

#### Success is so Painful!

- The i386 and i486 are once again successful, even amongst simpler, faster, and cheaper RISC CPUs. Intel manages to adapt again

- In 1995 Intel introduces their first pipelined version of the x86 ISA (Pentium) adapting many RISC concepts and adding a few new ones.

- Nonetheless, x86 starts to feel growing pains again as 32-bit architectures run out of space for code and data

• Around 2005, Intel introduces a 64-bit Pentium D, Core 2, Core i3, i5, and i7 archetectures

#### Lessons Learned

- Instruction Set Architectures would rather Evolve than be Reinvented!

- While developing new CPU hardware is expensive, it pales in comparison to developing software. Thus, maintaining backward-compatibility has been one of Intel's secrets of success.

Fear not padawan, still one hope remains

- Beauty does not equal Truth!

- Just because instructions are ugly does not mean that they can't accomplish the task. Conversely, if a task gets done, no one cares if it was done in an ugly or beautiful manner

- Birds in the hand are unlikely to become jet liners!

- It is always better to apply your cleverness to making existing customers happier with what they've already done, than trying to convince them they should start over doing it a better way.

#### Revisiting 1,2, and 3 Operands

- Operands the variables needed to perform an instruction's operation

- Two types in Intel's history

- One address: ADD C  $\# A \leftarrow A + C$

- Two address: ADD CX,DX # CX  $\leftarrow$  CX + DX

- Three types in the MIPS ISA:

- Three Address (Registers only!):

- add \$2, \$3, \$4 # operands are the "Contents" of a register

- Immediate:

- addi \$2,\$2,1 #  $2^{nd}$  source operand is part of the instruction

- Register-Indirect:

- lw \$2, 12(\$28) # source operand is in memory

- sw \$2, 12(\$28) # destination operand is memory

- Simple, but is it enough?

# Common "Addressing Modes"

MIPS can do these with appropriate choices for Ra and const

- Absolute (Direct): Iw \$8, 1000(\$0)

- Value = Mem[constant]

- Use: accessing static data

- Indirect: Iw \$8 0(\$9)

- Value = Mem[Reg[x]]

- Use: pointer accesses

- **Displacement:** lw \$8, 16(\$9)

- Value = Mem[Reg[x] + constant]

- Use: access to local variables

- Indexed:

- Value = Mem[Reg[x] + Reg[y]]

- Use: array accesses (base+index)

- Memory indirect:

- Value = Mem[Mem[Reg[x]]]

- Use: access thru pointer in mem

- Autoincrement:

- Value = Mem[Reg[x]]; Reg[x]++

- Use: sequential pointer accesses

- Autodecrement:

- Value = Reg[X]--; Mem[Reg[x]]

- Use: stack operations

- Scaled:

- Value = Mem[Reg[x] + c + d\*Reg[y]]

- Use: array accesses (base+index)

Argh! Is the complexity worth the cost? Need a cost/benefit analysis!

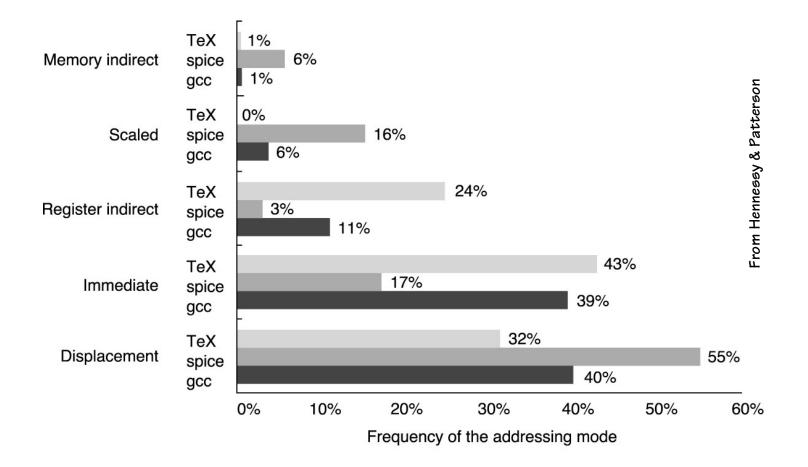

### Memory Operands: Usage

#### Usage of different memory operand modes

© 2003 Elsevier Science (USA). All rights reserved.

#### **Real-World Addressing**

- What we want:

- In general, the contents of a specific memory location

- How we get it? Let's look at high-level constructs!

- Examples: "MIPS Assembly" main: addiu \$sp,\$sp,-16 There's "x: lw \$24,x "C" sll \$15,\$24,2 Here's the int x = 5; lw \$15,data(\$15)\_\_

sw \$15,-4+16(\$sp) 👤 🦳 array access int data[10]; Where's y? main() { addiu \$24,\$24,1 int v; sw \$24,x v = data[x];move \$2,\$0 x = x + 1;addiu \$sp,\$sp,16 } jr \$31 .word 0x5**x**: data: .space 10

- Caveats

- In practice \$gp is often used as a base address for all variables

- Can only address the first and last 32K of memory this way

- Sometimes generates a two instruction sequence:

```

lui $1,xhighbits

lw $2,xlowbits($1)

```

#### Next Time

- More about how "C"

- How and where does it allocate variables?

- How are common high-level constructs converted to assembly language?

- if () { } else{ };

- for (;;) { }

- while () { }

- do { } while ();

- +=, ++, -=, &, &&

- myfunc(arg1, arg2)